# **OKI** Semiconductor **MSM7603 Evaluation Board**

## Echo Canceller

# **GENERAL DESCRIPTION**

This evaluation board has been developed to evaluate the characteristics of the echo cancellers MSM7603-003 (28-pin SSOP) and MSM7603B-003 (28-pin SSOP).

The MSM7603 and MSM7603B can support the both 3V and 5V supply voltages. This evaluation board can also support the both voltages if the PCM CODEC is replaced.

This evaluation board is provided with both analog and digital input/output interfaces, so that it can support a wide range of evaluation circuits.

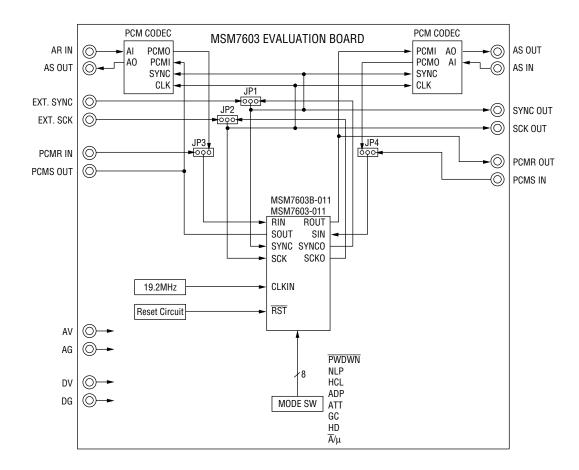

# **BLOCK DIAGRAM**

#### **SPECIFICATIONS**

|                                           |                 | 3V C                                                                                                                                                                                                                       | peration          | 5V Operation            |             |  |                     |  |  |

|-------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------|-------------|--|---------------------|--|--|

| CODEC                                     |                 | MSM7566 : μ–law                                                                                                                                                                                                            |                   | MSM7543 : μ–law         |             |  |                     |  |  |

| /ISM7603 : μ–law                          |                 | MSM7567 : A–law                                                                                                                                                                                                            |                   | MSM7544 : A–law         |             |  |                     |  |  |

| Analog input block                        |                 |                                                                                                                                                                                                                            |                   |                         |             |  |                     |  |  |

| Max. input level                          |                 | 1.4V <sub>P-P</sub>                                                                                                                                                                                                        |                   | 2.4V <sub>P-P</sub>     |             |  |                     |  |  |

| Input impedance                           |                 | 6                                                                                                                                                                                                                          | 00Ω               | 600Ω                    |             |  |                     |  |  |

| Analog output block                       |                 |                                                                                                                                                                                                                            |                   |                         |             |  |                     |  |  |

| Output level                              |                 | 21                                                                                                                                                                                                                         | δV <sub>P-P</sub> | 2.6V <sub>P-P</sub>     |             |  |                     |  |  |

| Output impedance                          |                 | 600Ω                                                                                                                                                                                                                       |                   | 600Ω                    |             |  |                     |  |  |

| Digital input                             | VIH             | 2.0V to V <sub>DD</sub>                                                                                                                                                                                                    |                   | 2.4V to V <sub>DD</sub> |             |  |                     |  |  |

| Digital iliput                            | V <sub>IL</sub> | 0 te                                                                                                                                                                                                                       | o 0.5V            | 0 to 0.8V               |             |  |                     |  |  |

| Digital output                            | V <sub>OH</sub> | 2.2V to V <sub>DD</sub>                                                                                                                                                                                                    |                   | 4.2V to V <sub>DD</sub> |             |  |                     |  |  |

| Digital output                            | V <sub>OL</sub> | 0 to 0.4V                                                                                                                                                                                                                  |                   | 0 to 0.6V               |             |  |                     |  |  |

| Supply voltage                            |                 | 2.7V to 3.6V                                                                                                                                                                                                               |                   | 4.5V to 5.5V            |             |  |                     |  |  |

| Operating temperature                     |                 | –30 to 85°C                                                                                                                                                                                                                |                   |                         |             |  |                     |  |  |

| Board size                                |                 | 18 × 11cm                                                                                                                                                                                                                  |                   |                         |             |  |                     |  |  |

| Echo canceller characteris                | stics           |                                                                                                                                                                                                                            |                   |                         |             |  |                     |  |  |

| Echo attenuation<br>Cancelable delay time |                 | 30dB Input signal: White noise–10 dBm0                                                                                                                                                                                     |                   |                         |             |  |                     |  |  |

|                                           |                 | ERL: 6 dB(echo volume=-10 dB0-6 dB=-16 dBm0)<br>Echo delay time: 2 ms<br>Control mode: NLP, ATT, GC, and OFF<br>59ms(max.): This is a calculated value.<br>The echo attenuation of 30dB is possible by using<br>about 5ms. |                   |                         |             |  |                     |  |  |

|                                           |                 |                                                                                                                                                                                                                            |                   |                         | Basic clock |  | 19.2MH <sub>Z</sub> |  |  |

2

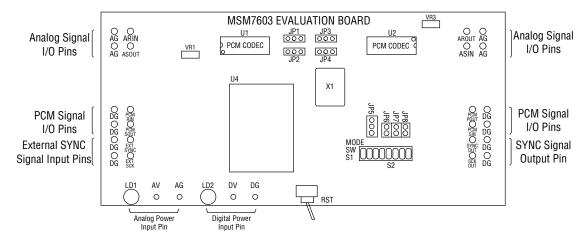

#### **EXTERNAL VIEW/PARTS ARRANGEMENT**

### **DESCRIPTION OF PINS/PARTS**

| Pin Name | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A RIN    | I   | Input pin for RIN signal when analog interface is used. Input analog signal is converted to PCM(A/D conversion) by U1 PCM CODEC and used as RIN signal of MSM7603/MSM7603B. Set JP3(RIN SEL) to ANLG when using ARIN input.(See JP3)                                                                                                                                                                                                                     |

| A ROUT   | 0   | Output pin for ROUT signal when analog interface is used.<br>This pin outputs analog signals D/A–converted from ROUT signal(PCM) of MSM7603/MSM<br>7603B by U2 PCM CODEC.<br>The signal level can be amplified by about 0 to +12 dB using variable resistor VR3.                                                                                                                                                                                         |

| A SIN    | I   | Input pin for SIN signal when analog interface is used,<br>Input analog signal is converted to PCM(A/D conversion) by U2 PCM CODEC and used<br>as SIN signal of MSM7603/MSM7603B.<br>Set JP4(SIN SEL) to ANLG when using ASIN input.(See JP4.)                                                                                                                                                                                                           |

| A SOUT   | 0   | Output pin for SOUT signl when analog interface is used.<br>This pin outputs analog signals D/A–converted from SOUT signal(PCM) of MSM7603/MSM<br>7603B by U1 PCM CODEC.<br>This signal level can be amplified by about 0 to +12 dB using variable resistor VR1.                                                                                                                                                                                         |

| PCM RIN  | I   | Input pin for RIN signal when PCM interface is used.<br>This input signal is used directly as RIN signal of MSM7603/MSM7603B. Input positive phase<br>signal to this pin. Set JP3(RIN SEL) to PCM when using PCM RIN.(See JP3.) Use of PCM<br>interface requires synchronization with destination.<br>Use external synchronization(EXT.SYNC or EXT.SCK) or synchronizing signal output(SYNC<br>OUT or SCK OUT) for the synchronization with destination. |

| PCM ROUT | 0   | Output pin for ROUT signal when PCM interface is used. This pin outputs ROUT signal(positive phase) of MSM7603/MSM7603B directly. Use of PCM interface requires synchronization with destination. Use external synchronization(EXT.SYNC or EXT.SCK) or synchronizing signal output(SYNC OUT or SCK OUT) for the synchronization with destination.                                                                                                        |

| Pin Name | I/O | Description                                                                                     |

|----------|-----|-------------------------------------------------------------------------------------------------|

| PCM SIN  | I   | Input pin for SIN signal when PCM interface is used.                                            |

|          |     | This input signal is used as SIN signal of MSM7603/MSM7603B as is. Input positive phase signal  |

|          |     | to this pin. Set JP4(SIN SEL) to PCM when using PCM SIN.(See JP4.) Use of PCM interface         |

|          |     | requires synchronization with destination. Use enternal synchronization(EXT.SYNC or EXT.SCK) or |

|          |     | synchronizing signal output (SYNC OUT or SCK OUT) for the synchronization with destination.     |

| PCM SOUT | 0   | Output pin for SOUT signal when PCM interface is used.                                          |

|          |     | This pin outputs SOUT signal of MSM7603/MSM7603B directly at positive phase signal.             |

|          |     | Use of PCM interface requires synchronization with destination. Use external synchronization    |

|          |     | (EXT.SYNC or EXT.SCK) or synchronizing signal output(SYNC OUT or SCK OUT) for the               |

|          |     | synchronization with destination.                                                               |

| EXT.SYNC | I   | Input pin for EXT.SYNC signal when external synchronization is required.                        |

|          |     | EXT.SYNC signal is used as synchronizing signal when PCM interface is used.(See JP1.)           |

|          |     | Input 8kHz SYNC(positive phase) to this pin.                                                    |

| EXT.SCK  | I   | Input pin for EXT.SCK signal when external when external synchronization is required.           |

|          |     | EXT.SCK signal is used as synchronizing signal when PCM interface is used.(See JP2.)            |

|          |     | Input 64 to 2048 kHz SCK(positive phase) signal to this pin.                                    |

| SYNC OUT | 0   | Output pin for synchronizing SYNC signal.                                                       |

|          |     | SYNC OUT signal is used as synchronizing signal when PCM interface is used.                     |

|          |     | This pin outputs SYNC signal(positive phase) selected by JP1.                                   |

| SCK OUT  | 0   | Outpit pin for synchronizing SCK signal.                                                        |

|          |     | SCK OUT signal is used as synchronizing signal when PCM interface is used.                      |

|          |     | This pin outputs SCK signal(positive phase) selected by JP2.                                    |

| AV       | Ι   | Power supply for analog system.                                                                 |

|          |     | Input 3V or 5V just like power supply for digital system.                                       |

|          |     | Select PCM CODEC(U1/U2) according to selected supply voltage.                                   |

|          |     | 3V operation: MSM7566/MSM7567                                                                   |

|          |     | 5V operation: MSM7543/MSM7544                                                                   |

| AG       | Ι   | GND for analog system.                                                                          |

|          |     | Basically this GND is separated from GND for digital system.                                    |

| DV       | Ι   | Power supply for digital system.                                                                |

|          |     | Input 3V or 5V just like power supply for analog system.                                        |

|          |     | Select PCM CODEC(U1/U2) according to selected supply voltage.                                   |

|          |     | 3V operation: MSM7566/MSM7567                                                                   |

|          |     | 5V operation: MSM7543/MSM7544                                                                   |

| DG       | I   | GND for digital system.                                                                         |

|          |     | Basically, this GND is separated from GND for analog system.                                    |

**OKI** Semiconductor

| Part No./Name |                    | Description                                                                                     |  |  |  |

|---------------|--------------------|-------------------------------------------------------------------------------------------------|--|--|--|

| U1            | PCM CODEC          | μ–law or A-law CODEC is used.                                                                   |  |  |  |

| U2            |                    | Select PCM CODEC according to selected supply voltage and then set a mode with MODE SW 8.       |  |  |  |

|               |                    | 3V operation: MSM7566 (μ-law) / MSM7567 (A-law)                                                 |  |  |  |

|               |                    | 5V operation: MSM7543 (μ-law) / MSM7544 (A-law)                                                 |  |  |  |

|               |                    | Note that U2 parts are reversely placed.                                                        |  |  |  |

| U4            | MSM7603-003        | Mount MSM7603-003 or MSM7603B-003.                                                              |  |  |  |

|               | IC socket          |                                                                                                 |  |  |  |

| X1            | Crystal oscillator | 19.2 MHz is used. Select 5V or 3V crystal oscillator according to power supply used.            |  |  |  |

| VR1           | ASOUT volume       | Variable resistor to adjust output level of ASOUT by about 0 to +12 dB.                         |  |  |  |

| VR3           | AROUT volume       | Variable resistor to adjust output level of AROUT by about 0 to +12 dB.                         |  |  |  |

| JP1           | SYNC SEL           | SYNC select pin.                                                                                |  |  |  |

|               | jumper             | This pin selects internal SYNC signal or external SYNC signal. Set this JP1 just like           |  |  |  |

|               |                    | JP2(SCK selector).                                                                              |  |  |  |

|               |                    | SYNC SEL<br>EXT/INT                                                                             |  |  |  |

|               |                    | JP1 Internal SYNC mode: SYNC0 signal that is output from MSM7603 or MSM7603B is used.           |  |  |  |

|               |                    | EXT/INT<br>JP1                                                                                  |  |  |  |

|               |                    |                                                                                                 |  |  |  |

| JP2           | SCK SEL            | SCK select pin.                                                                                 |  |  |  |

|               | jumper             | This pin selects internal SCK signal or external SCK signal. Set this JP2 just like             |  |  |  |

|               |                    | JP1(SYNC selector).                                                                             |  |  |  |

|               |                    | SCK SEL                                                                                         |  |  |  |

|               |                    | EXT/INT   JP2   Internal SCK mode: SCK0 signal that is output from MSM7603 or MSM7603B is used. |  |  |  |

|               |                    | EXT/INT<br>JP2                                                                                  |  |  |  |

| Part No./Name |                        | Description                                                                                                                                    |  |  |  |

|---------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| JP3           | RIN SEL                | RIN select pin.                                                                                                                                |  |  |  |

|               | jumper                 | This pin selects signal to be input to RIN of MSM7603/MSM7603B.                                                                                |  |  |  |

|               |                        | PCM/ANLG<br>JP3 COC Analog input mode: PCM signal is used, which is converted (A/D conversion)<br>by U1 (PCM CODEC) from analog signal that is |  |  |  |

|               |                        | input from APINI nin                                                                                                                           |  |  |  |

|               |                        | JP3 PCM input mode: PCM signal is used, which is input from RIN pin.                                                                           |  |  |  |

| JP4           | SIN SEL                | SIN select pin.                                                                                                                                |  |  |  |

|               | jumper                 | This pin selects signals to be input to SIN of MSM7603/MSM7603B.                                                                               |  |  |  |

|               |                        | SIN SEL PCM input mode: PCM signal is used, which is converted (A/D conversion)   JP4 by U1(PCM CODEC) from analog signal that is input        |  |  |  |

|               |                        | ANLG/PCM from ASIN pin.<br>JP4 COO PCM input mode: PCM signal is used, which is input from RIN pin.                                            |  |  |  |

| JP5           | CLK SEL                | This pin is not used.                                                                                                                          |  |  |  |

|               | jumper                 | Set this pin to OPEN.                                                                                                                          |  |  |  |

| JP6           | OF SEL                 | These pins are not used.                                                                                                                       |  |  |  |

| JP7           | jumper                 | OF SEL                                                                                                                                         |  |  |  |

| JP8           |                        | Set these pins all to OPEN.                                                                                                                    |  |  |  |

| S2            | RST SW                 | Resets MSM7603/MSM7603B. Be sure to reset MSM7603/MSM7603B after power is turned on.                                                           |  |  |  |

| LD1           | Analog power<br>light  | Goes on after analog power input.                                                                                                              |  |  |  |

| LD2           | Digital power<br>light | Goes on after digital power input.                                                                                                             |  |  |  |

#### **OKI** Semiconductor

#### **MSM7603**

| Part No./Name |         |                                                                                               | Description |      |                                                                                                                                                        |  |

|---------------|---------|-----------------------------------------------------------------------------------------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| S1            | MODE SW | Sets up control pins of MSM7603.<br>꽃룩ᇊ ᇦ 뇤 용 등 홎                                             |             |      |                                                                                                                                                        |  |

|               |         | 1 2 3 4 5 6 7 8<br>OPEN OPEN OPEN                                                             |             |      |                                                                                                                                                        |  |

|               |         | N ON OFF<br>Alaw / µLaw<br>OFF/ON<br>OFF/ON<br>OFF/ON<br>OFF/ON<br>OFF/ON<br>OFF/ON<br>OFF/ON |             |      |                                                                                                                                                        |  |

|               |         | MO                                                                                            | MODE SW     |      | Operation                                                                                                                                              |  |

|               |         | 1                                                                                             | PDWN        | ON   | Sets power down mode. This switch stops MSM7603 operation to reduce power consumption.                                                                 |  |

|               |         |                                                                                               |             | OPEN | Sets normal mode.                                                                                                                                      |  |

|               |         | 2                                                                                             | NLP         | ON   | Turns center clip off.                                                                                                                                 |  |

|               |         |                                                                                               |             | OPEN | Turns center clip on.<br>When SOUT output is –57 dBm0 or lower, this switch outputs<br>min. positive value(FFh) forcibly to reduce idle circuit noise. |  |

|               |         | 3                                                                                             | HCL         | ON   | Sets normal mode to cancel echo.                                                                                                                       |  |

|               |         |                                                                                               |             | OPEN | Sets through mode. Data that was input to RIN and SIN are output to ROUT and SOUT in through mode respectively.                                        |  |

|               |         | 4                                                                                             | ADP         | ON   | Sets normal mode to update AFF coefficient.                                                                                                            |  |

|               |         |                                                                                               |             | OPEN | Sets coefficient fix mode to stop updating of AFF coefficient<br>and operates LSI device according to stop time coefficient.                           |  |

|               |         | 5                                                                                             | ATT         | ON   | Turns ATT on. Attenuator(6 dB)prepared in RIN and SOUT<br>is inserted in MSM7603 according to input status.<br>Refer to data sheet for operation.      |  |

|               |         |                                                                                               |             | OPEN | Turns ATT off.                                                                                                                                         |  |

|               |         | 6                                                                                             | GC          | ON   | Turns GC off.                                                                                                                                          |  |

|               |         |                                                                                               |             | OPEN | Controls signal level to be within 0 to 8.5 dB using gain controller prepared in RIN. Level control is validated at around –24 dBm0.                   |  |

|               |         | 7                                                                                             | HD          | ON   | Turns HD on.<br>This switch detects and cancels howling.                                                                                               |  |

|               |         |                                                                                               |             | OPEN | Turns HD off.                                                                                                                                          |  |

|               |         | 8                                                                                             | Α/μ         | ON   | A-law mode                                                                                                                                             |  |

|               |         |                                                                                               |             | OPEN | μ-law mode                                                                                                                                             |  |

#### **USING METHOD**

1) Set jumper pins suitable for the circuit to be connected.

(1) Set the synchronizing signal (external or internal synchronization).

| JP1 (SYNC SEL) | EXT/INT |

|----------------|---------|

| JP2 (SCK SEL)  | EXT/INT |

(2) Set the input signals(PCM or analog). JP3 (RIN SEL) PCM/ANLG JP4 (SIN SEL) ANLG/PCM

2) Adjust the analog output level.

In this evaluation board, the analog output level can be adjusted by about 0 to +12dB using VR3 and VR1.

3V CODEC (MSM7566/MSM7567) should be adjusted because CODER side and DECODER side levels are different.

Set input and output levels using a level meter or an oscilloscope, so that they are equal or have levels specified.

3) Connect the power supply and the ground (GND).

In this board, basically analog and digital systems are separated from each other. Since the characteristics of an analog circuit affect the characteristics of an echo canceller, use an analog power supply/GND with less noise.

A power supply/GND with less noise can be used commonly for both analog and digital systems.

4) Set the MODE switch to desired mode.

Note: Do not turn the power on while the MODE SW1 (PWDWN SW) is on (in the power down mode).

Power down should be made after more than 10 basic clocks are input. This is to stabilize the internal status.

5) The setting of the MSM7603 evaluation board is complete.

Input signals from the set interface to start the test.

Note: Be sure to reset the MSM7603 after the power is turned on.

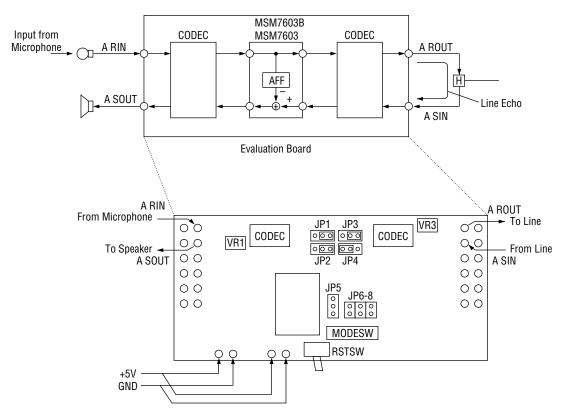

• Use example 1: Line echo cancellation (to cancel the line echo caused by an input from a microphone)

Setups: Single chip, analog interface, and internal synchronization

- (1) Set the evaluation board as follows.

- Set JP1 and JP2 to INT to set the internal synchronization mode.

- Set JP3 and JP4 to ANLG to set the analog interface mode.

- Make sure the MODE switch 1(PWDWN SW) is set to OPEN.

- (2) Connect the MSM7603 to a power supply and adjust the analog output level. Reset the MSM7603 after the power is turned on. Tone signal may be used to adjust the analog output level. In the test, however, be sure to use white noise or voice.

- (3) Connect the inputs/outputs of the MSM7603 to the test system and start the test. Reset the MSM7603 after the power is turned on.

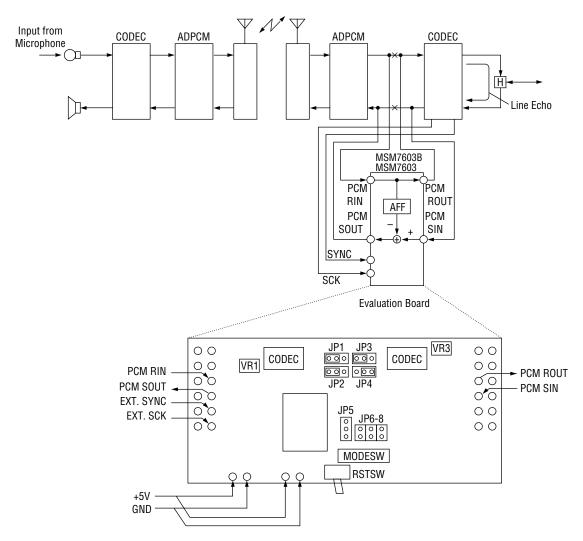

• Use example 2: Connecting an echo cancellor to an existing PCM circuit and checking the effect of the echo canceller.

Setups: PCM interface and external synchronization

- (1) Set the evaluation board as follows.

- Set JP1 and JP2 to EXT to set the external synchronization mode.

- Set JP3 and JP4 to PCM to set the PCM interface mode.

- Make sure the MODE switch 1(PWDWN SW) is set to OPEN.

- (2) Connect the MSM7603 to a power supply and adjust the analog output level. Reset the MSM7603 after the power is turned on. Tone signal may be used to adjust the analog output level. In the test, however, be sure to use white noise or voice.

- (3) Connect the inputs/outputs of the MSM7603 to the test system and start the test. Reset the MSM7603 after the power is turned on.

NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit and assembly designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to:traffic control, automotive, safety, aerospace, nuclear power control, and medical, including life support and maintenance.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents cotained herein may be reprinted or reproduced without our prior permission.

- 9. MS–DOS is a registered trademark of Microsoft Corporation.

Copyright 1997 Oki Electric Industry Co., Ltd.