### OKI

# MSM66577 Family

### User's Manual

**CMOS 16-bit microcontroller**

Preliminary

FIRST EDITION ISSUE DATE: Dec. 2000

PEUL66577-01

#### NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 2000 Oki Electric Industry Co., Ltd.

#### Preface

This user's manual describes the hardware of Oki-original CMOS 16-bit microcontrollers MSM66577 family. In addition to this manual, Oki also provides the following manuals which should be read with regard to the MSM66577 family.

nX-8/500S Core Instruction Manual

- nX-8/500S core instruction set

- Addressing modes

CC665S User's Manual

- Optimized compiler CC665S operation

- C-language specifications in CC665S

CL665S User's Manual

• Compiler loader CL665S operation

RTL665S Run Time Library Reference

• C run time library explanation

MAC66K Assembler Package User's Manual

- Package overview

- RAS66K (relocatable assembler) operation

- RAS66K assembly language explanation

- RL66K (linker) operation

- LIB66K (librarian) operation

- OH66K (object converter) operation

Macroprocessor MP User's Manual

- MP operation

- Macro language

Ultra-66K/E502 User's Manual

- Ultra-66K (Emulator) explanation

- PathFinder-66K (Debugger) explanation

PW66K Flash Writer System User's Manual

• PW66K Flash Writer System operation

This document is subject to change without notice.

| Classification       | Notation                                                                                                                           | Description                                                                                                                                                                                                                                                                                              |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ■ Numeric value      | xxH<br>xxb                                                                                                                         | Represents a hexadecimal number<br>Represents a binary number                                                                                                                                                                                                                                            |

| ■ Unit               | Word, W<br>byte, B<br>nibble, N<br>mega-, M<br>kilo-, K<br>kilo-, k<br>milli-, m<br>micro-, µ<br>nano-, n<br>second, s<br>KB<br>MB | 1 word = 16 bits<br>1 byte = 2 nibbles = 8 bits<br>1 nibble = 4 bits<br>$10^{6}$<br>$2^{10} = 1024$<br>$10^{3} = 1000$<br>$10^{-3}$<br>$10^{-6}$<br>$10^{-9}$<br>second<br>1KB = 1  kilobyte = 1024  bytes<br>$1MB = 1 \text{ megabyte} = 2^{20} \text{ bytes}$<br>= 1,048,576  bytes                    |

| ■ Terminology        | "H" level<br>"L" level                                                                                                             | The signal level of the high side of the voltage;<br>indicates the voltage level of $V_{IH}$ and $V_{OH}$ described in the electrical characteristics.<br>The signal level of the low side of the voltage; indicates voltage level of $V_{IL}$ and $V_{OL}$ described in the electrical characteristics. |

| Register description | Opcode trap                                                                                                                        | Operation code trap. Occurs when an empty<br>area that has not been assigned an<br>instruction is fetched, or when an instruction<br>code combination that does not contain an<br>instruction is addressed.                                                                                              |

#### Notation

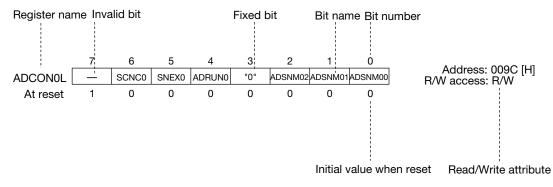

■ Register description

Invalid bit

#### Fixed bit

Read/write attribute :

:

:

When writing, always write the specified value. If read, the specified value will be read. Values of fixed bits are specified as "0" or "1." R indicates that reading is possible and W indicates that writing is possible.

Indicates that the bit does not exist. Writing into this bit is invalid.

#### Contents

#### Chapter 1 Overview

| 1.1 Overview                      | 1-1  |

|-----------------------------------|------|

| 1.2 Features                      | 1-1  |

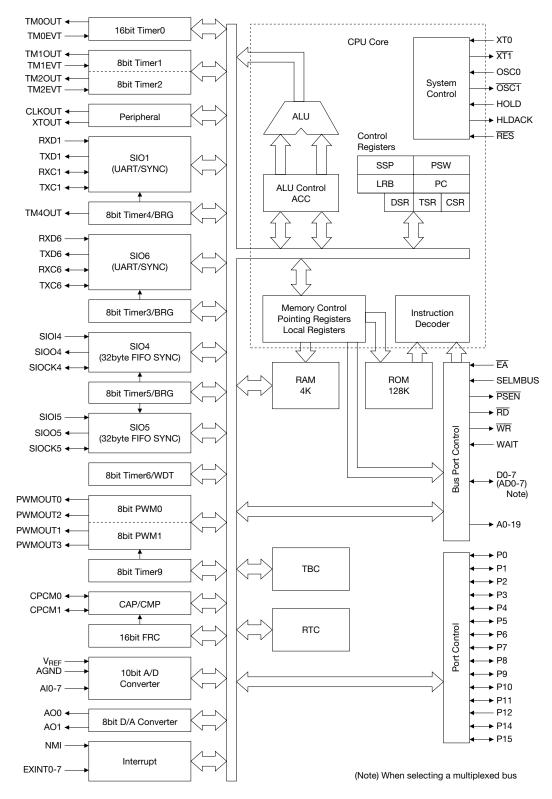

| 1.3 Block Diagram                 |      |

| 1.4 Pin Configuration             |      |

| 1.5 Pin Descriptions              |      |

| 1.5.1 Description of Each Pin     |      |

| 1.5.2 Pin Configuration           |      |

| 1.5.3 Connections for Unused Pins | 1-11 |

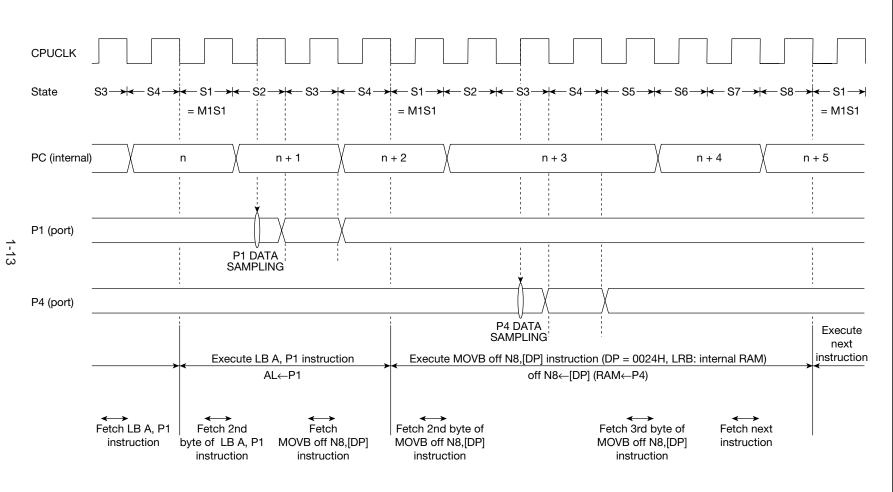

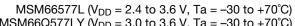

| 1.6 Basic Operational Timing      | 1-12 |

#### Chapter 2 CPU Architecture

| 2.1 | Ov  | erview                               | 2-1  |

|-----|-----|--------------------------------------|------|

| 2.2 | Me  | mory Space                           | 2-1  |

| 2.  | 2.1 | Memory Space Expansion               | 2-1  |

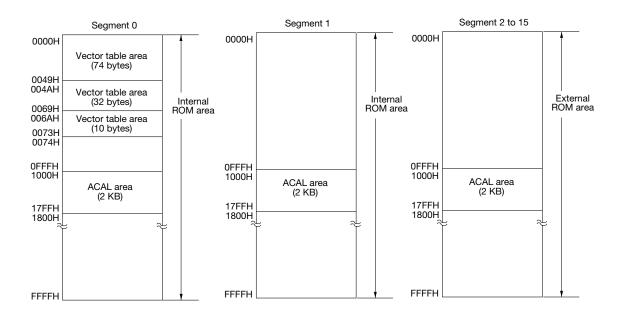

| 2.  | 2.2 | Program Memory Space                 |      |

|     | (1) | Accessing program memory space       |      |

|     | (2) | Vector table area                    | 2-5  |

|     | (3) | VCAL table area                      |      |

|     | (4) | ACAL area                            |      |

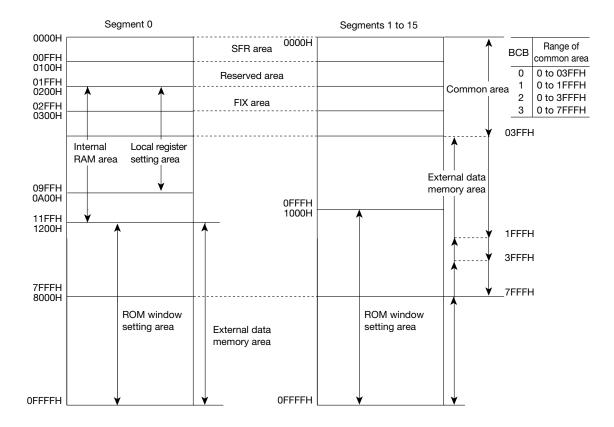

| 2.  | 2.3 | Data Memory Space                    |      |

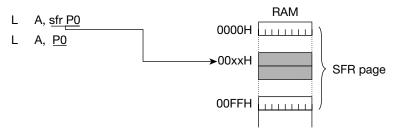

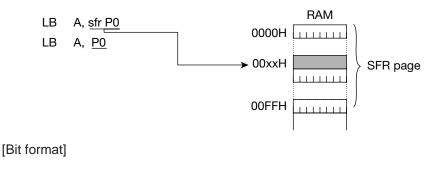

|     | (1) | Special function register (SFR) area | 2-12 |

|     | (2) | Reserved area                        | 2-12 |

|     | (3) | Internal RAM area                    |      |

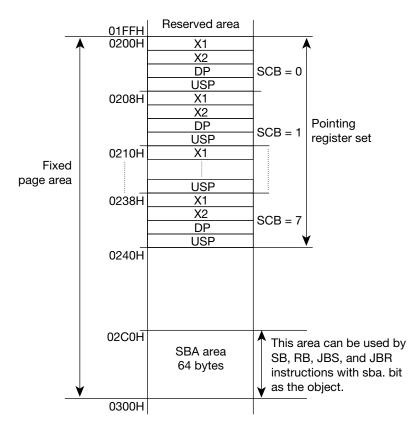

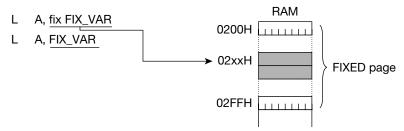

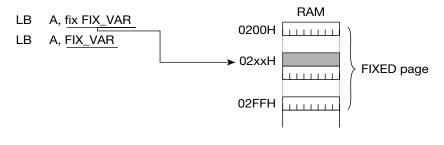

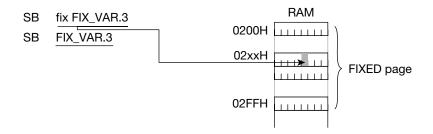

|     | (4) | Fixed page (FIX) area                | 2-12 |

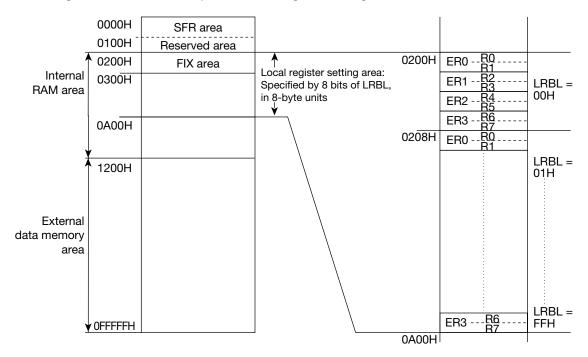

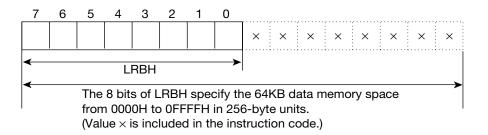

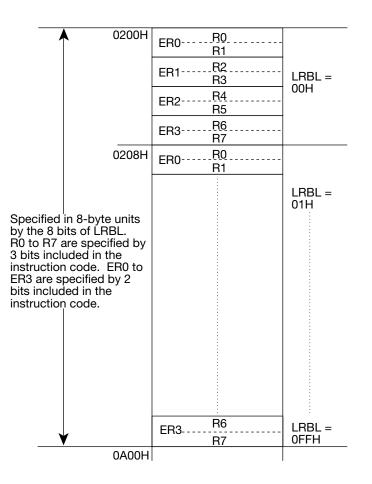

|     | (5) | Local register setting area          | 2-14 |

|     | (6) | External data memory area            | 2-14 |

|     | (7) | Common area                          | 2-15 |

| 2.  | 2.4 | Data Memory Access                   |      |

|     | (1) | Byte operations                      |      |

|     | (2) | Word operations                      |      |

| 2.3 | Re  | gisters                              |      |

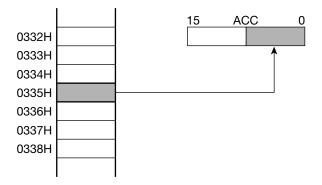

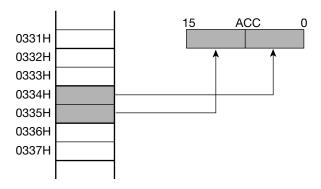

| 2.  | 3.1 | Arithmetic Register (ACC)            |      |

| 2.  | 3.2 | Control Registers                    | 2-18 |

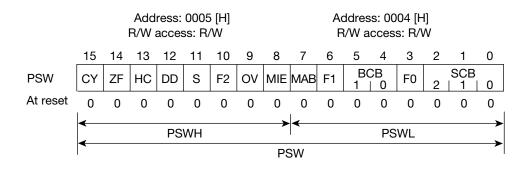

|     | (1) | Program status word (PSW)            |      |

|     | (2) | Program counter (PC)                 | 2-22 |

#### Contents-1

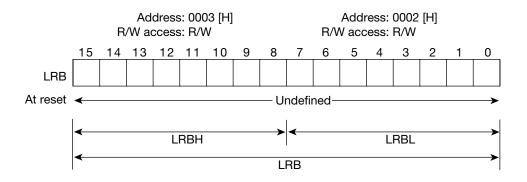

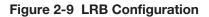

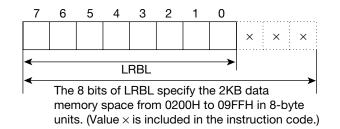

| (3)    | Local register base (LRB)              |      |

|--------|----------------------------------------|------|

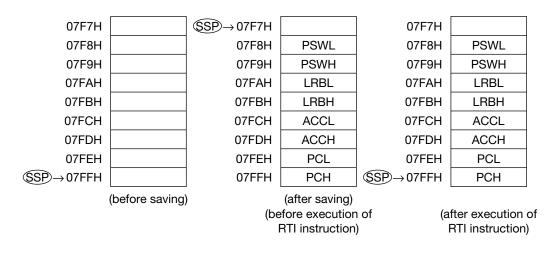

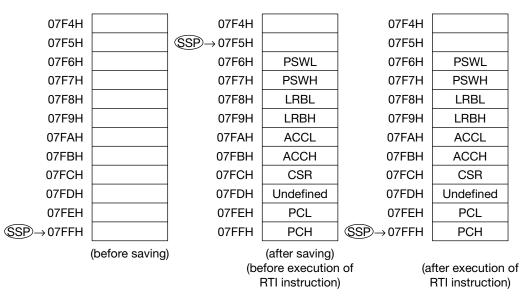

| (4)    | System stack pointer (SSP)             |      |

| 2.3.3  | Pointing Register (PR)                 |      |

| 2.3.4  | Local Registers (R0 to R7, ER0 to ER3) | 2-25 |

| 2.3.5  | Segment Registers                      |      |

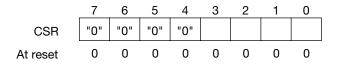

| (1)    | Code segment register (CSR)            |      |

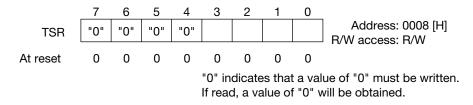

| (2)    | Table segment register (TSR)           |      |

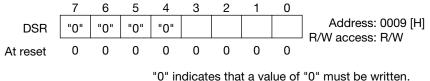

| (3)    | Data segment register (DSR)            |      |

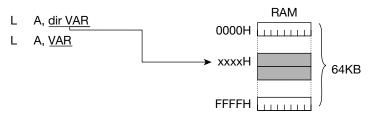

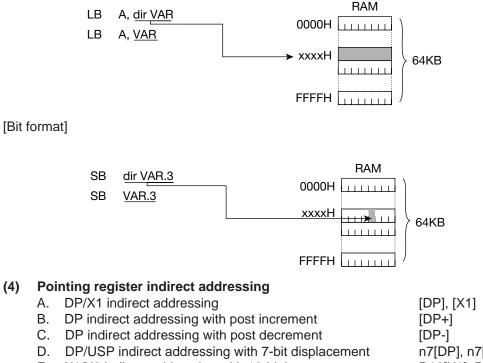

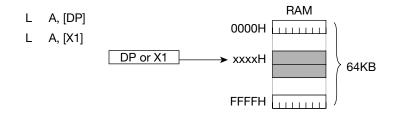

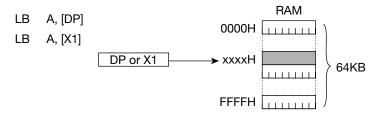

| 2.4 Ad | dressing Modes                         | 2-27 |

| 2.4.1  | RAM Addressing                         |      |

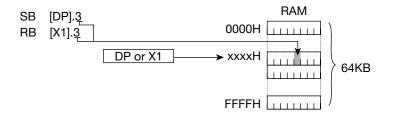

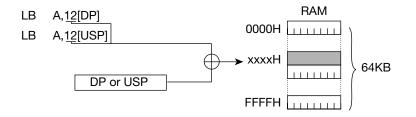

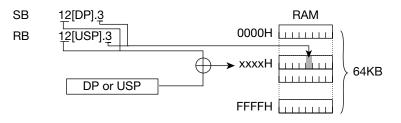

| (1)    | Register addressing                    |      |

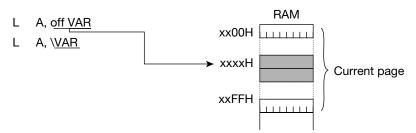

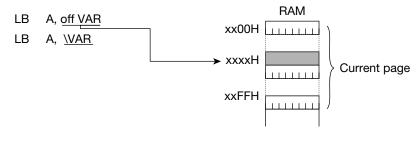

| (2)    | Page addressing                        |      |

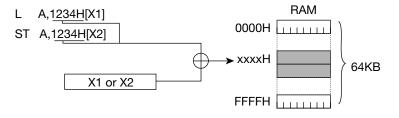

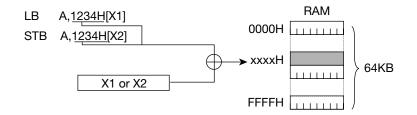

| (3)    | Direct data addressing                 |      |

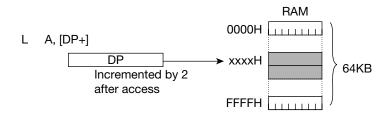

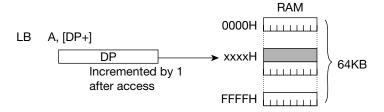

| (4)    | Pointing register indirect addressing  | 2-34 |

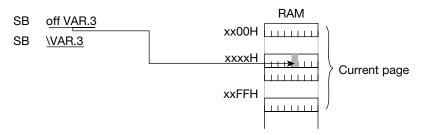

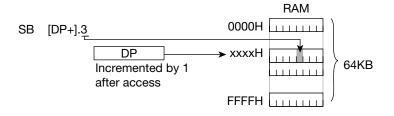

| (5)    | Special bit area addressing            | 2-41 |

| 2.4.2  | ROM Addressing                         |      |

| (1)    | Immediate addressing                   | 2-43 |

| (2)    | Table data addressing                  | 2-43 |

| (3)    | Program code addressing                | 2-45 |

| (4)    | ROM window addressing                  |      |

### Chapter 3 CPU Control Functions

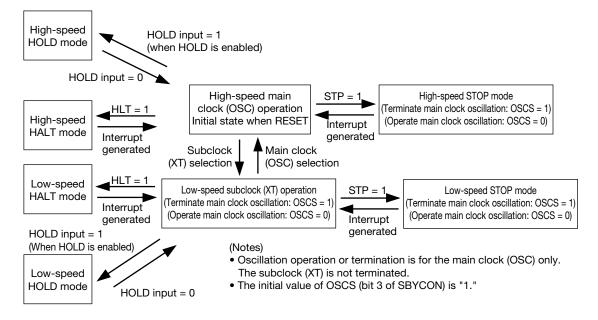

| 3.1 O\ | erview                                         |      |

|--------|------------------------------------------------|------|

| 3.2 St | andby Functions                                |      |

| 3.2.1  | Standby Function Registers                     |      |

| 3.2.2  | Description of Standby Function Registers      |      |

| (1)    | Stop code acceptor (STPACP)                    |      |

| (2)    | Standby control register (SBYCON)              |      |

| 3.2.3  | Examples of Standby Function Register Settings |      |

| •      | HALT mode setting                              |      |

| •      | HOLD mode setting                              |      |

| •      | STOP mode setting                              |      |

| 3.2.4  | Operation of Each Standby Mode                 |      |

| (1)    | HALT mode                                      |      |

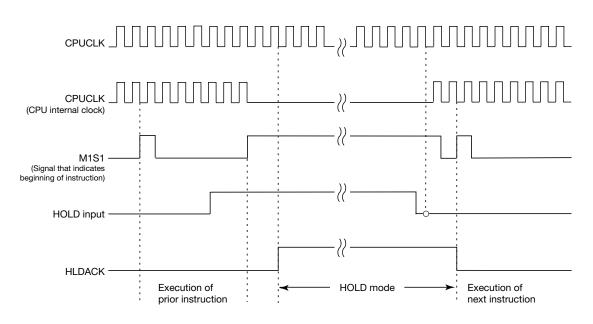

| (2)    | HOLD mode                                      |      |

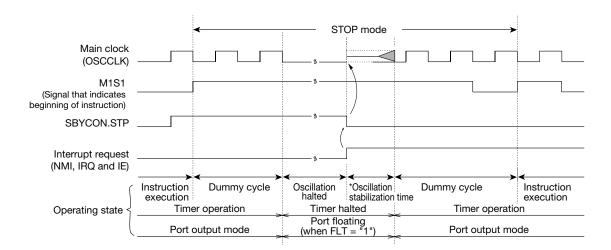

| (3)    | STOP mode                                      |      |

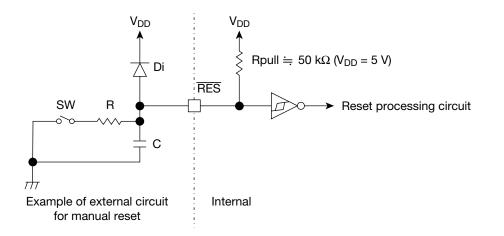

| 3.3 Re | set Function                                   | 3-10 |

#### Chapter 4 Memory Control Functions

| 4.1 | Overview                                | . 4-1 |

|-----|-----------------------------------------|-------|

| 4.2 | Memory Control Function Registers       | . 4-1 |

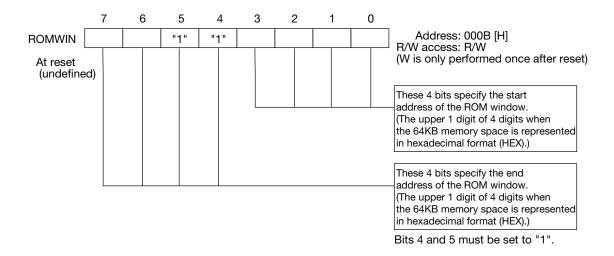

| 4.3 | ROM Window Function                     | . 4-2 |

| 4.4 | READY Function                          | . 4-4 |

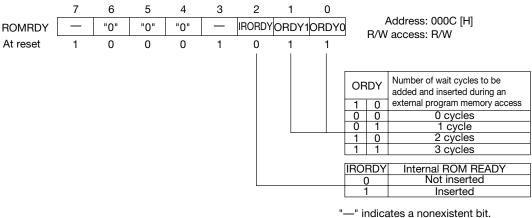

| 4.  | 4.1 ROM Ready Control Register (ROMRDY) | . 4-4 |

| 4.  | 4.2 RAM Ready Control Register (RAMRDY) | . 4-5 |

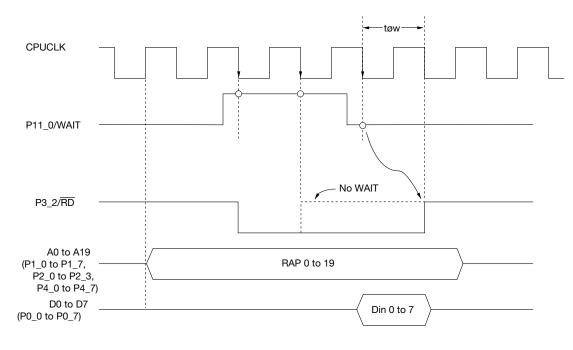

| 4.5 | WAIT Function                           | . 4-7 |

#### Chapter 5 Port Functions

| 5.1 C  | verview5-                                                                |

|--------|--------------------------------------------------------------------------|

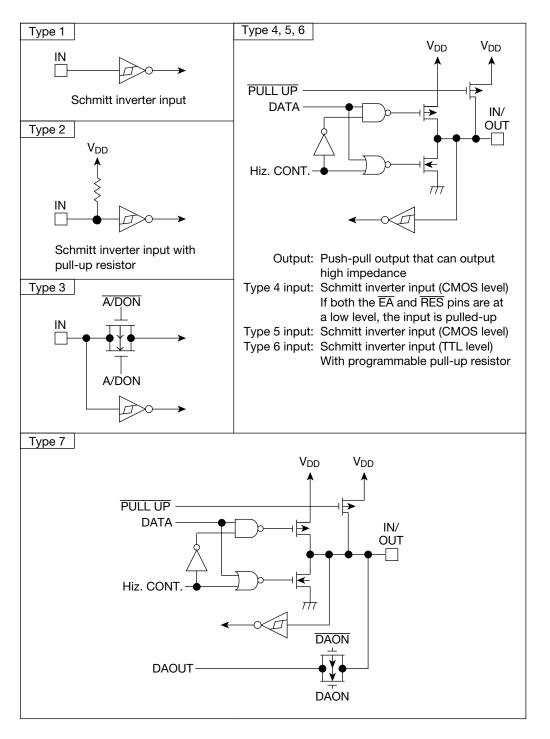

| 5.2 ⊦  | ardware Configuration of Each Port5-                                     |

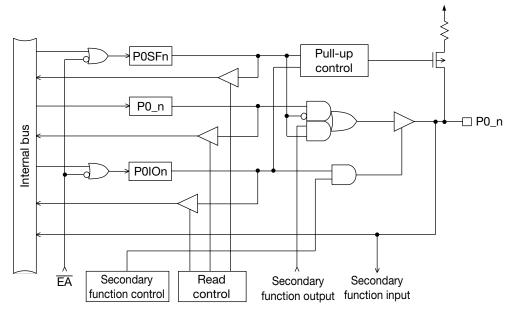

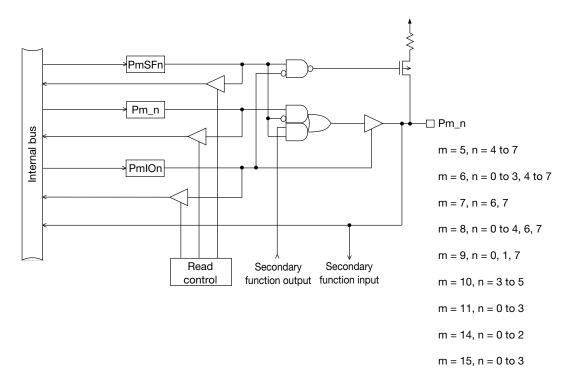

| 5.2.1  | Type A (P0)5-                                                            |

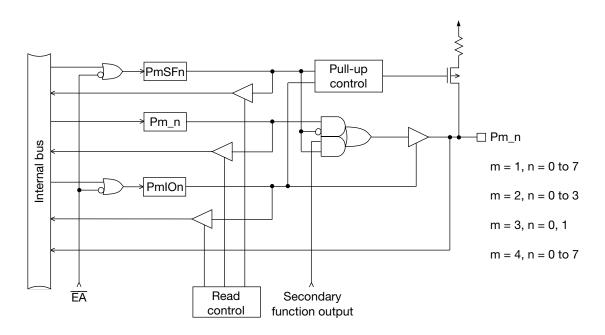

| 5.2.2  | Type B (P1, P2, P3_0, P3_1, P4)5-                                        |

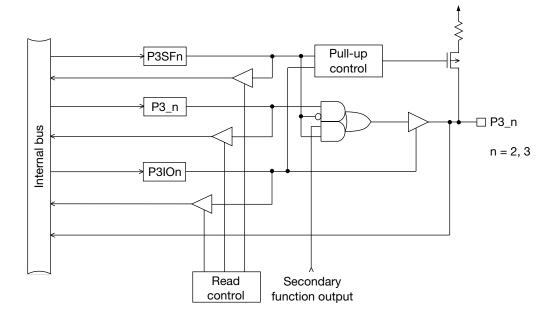

| 5.2.3  | Type C (P3_2, P3_3)5-                                                    |

| 5.2.4  | Туре D                                                                   |

|        | (P5, P6, P7, P8, P9, P10, P11, P14_0 to P14_2, P15)5-                    |

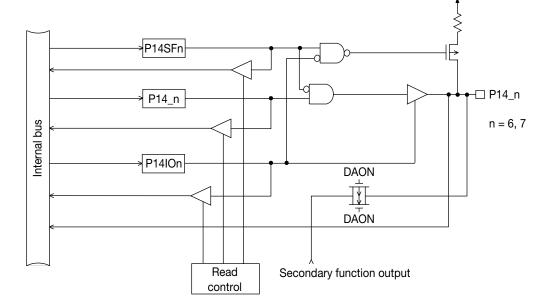

| 5.2.5  | Type E (P14_6, P14_7)5-                                                  |

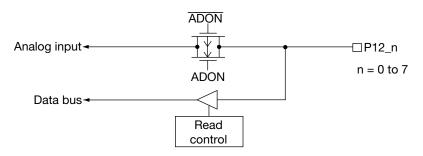

| 5.2.6  | Type F (P12)                                                             |

| 5.3 F  | ort Registers5-                                                          |

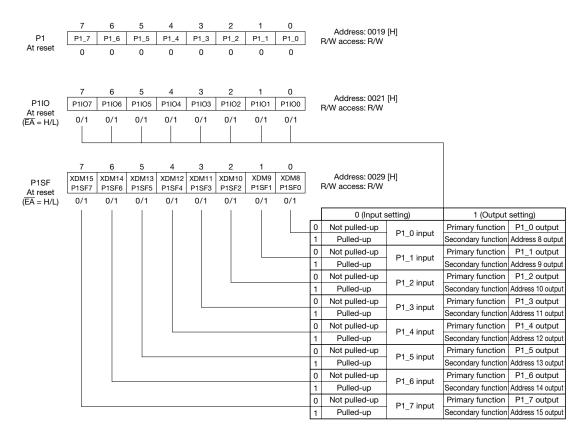

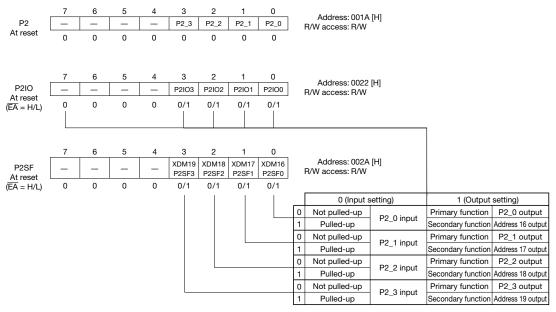

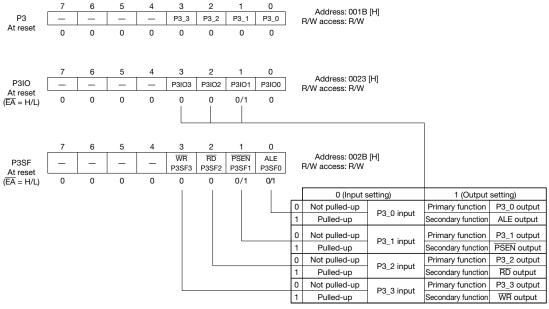

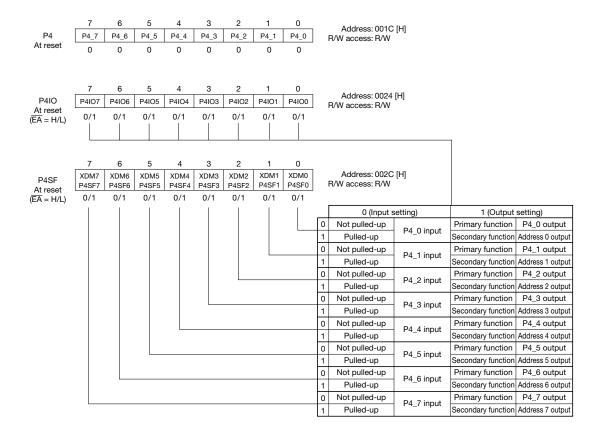

| 5.3.1  | Port Data Registers (Pn:n = 0 to 12, 14, 15)5-1                          |

| 5.3.2  | Port Mode Registers (PnIO:n = 0 to 11, 14, 15)5-1                        |

| 5.3.3  | Port Secondary Function Control Registers (PnSF:n = 0 to 11, 14, 15) 5-1 |

| 5.4 F  | ort 0 (P0)                                                               |

| 5.5 F  | ort 1 (P1)5-1                                                            |

| 5.6 F  | ort 2 (P2)                                                               |

| 5.7 F  | ort 3 (P3)5-1                                                            |

| 5.8 F  | ort 4 (P4)5-2                                                            |

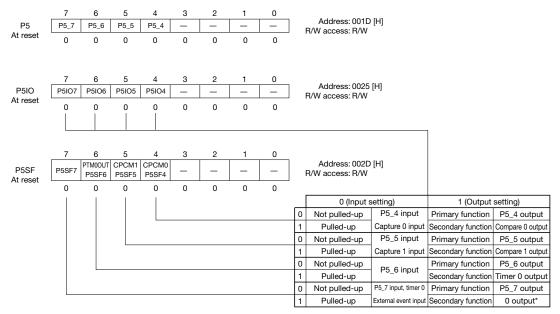

| 5.9 F  | ort 5 (P5)5-2                                                            |

| 5.10 F | ort 6 (P6)5-2-                                                           |

| 5.11 F | ort 7 (P7)5-2                                                            |

| 5.12 F | ort 8 (P8)                                                               |

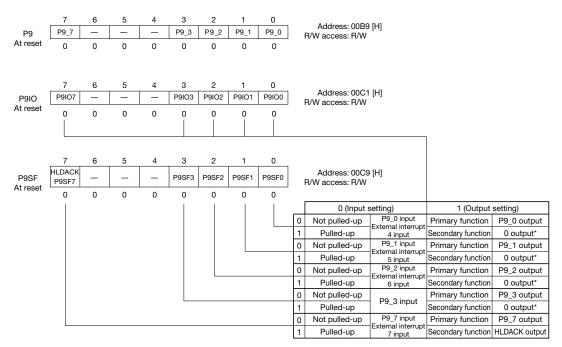

| 5.13 F | ort 9 (P9)5-3                                                            |

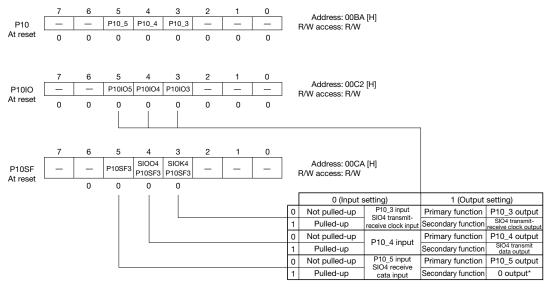

| 5.14 F | ort 10 (P10)                                                             |

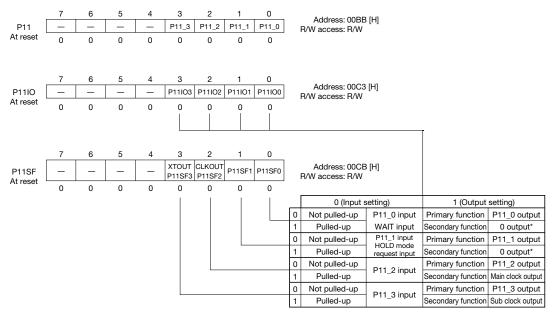

| 5.15 F | ort 11 (P11)5-3                                                          |

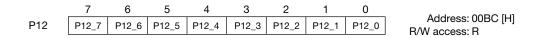

| 5.16 F | ort 12 (P12)5-3                                                          |

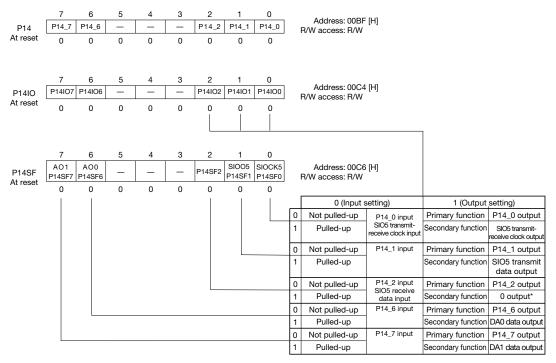

| 5.17 F | ort 14 (P14)5-3                                                          |

| 5.18 F | ort 15 (P15)5-3                                                          |

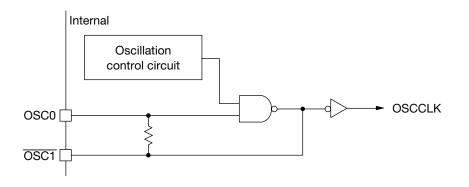

#### Chapter 6 Clock Oscillation Circuit

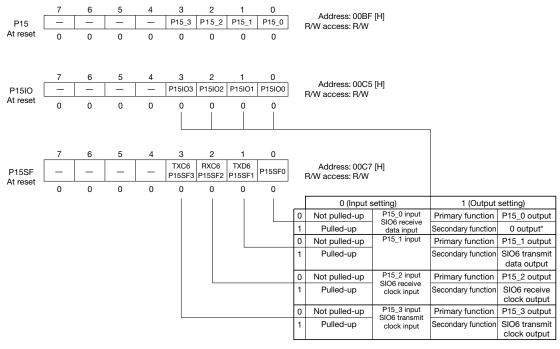

| 6.1 | Overview                                | 6-1 |

|-----|-----------------------------------------|-----|

| 6.2 | Clock Oscillation Circuit Configuration | 6-1 |

| 6.3 | Clock Oscillation Circuit Registers     | 6-2 |

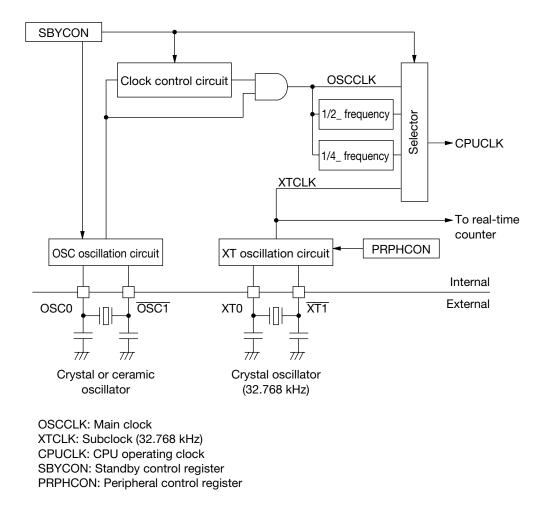

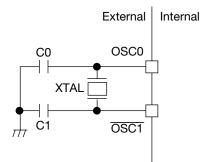

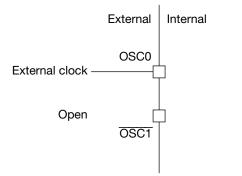

| 6.4 | OSC Oscillation Circuit                 | 6-2 |

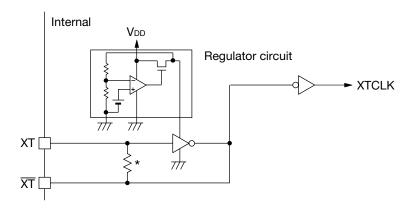

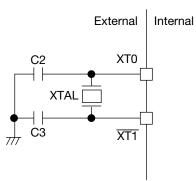

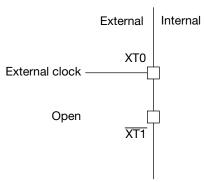

| 6.5 | XT Oscillation Circuit                  | 6-4 |

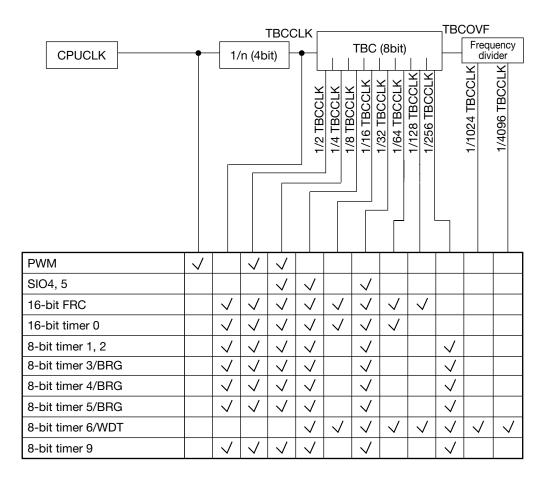

#### Chapter 7 Time Base Counter (TBC)

| 7.1 Overview                                           | 7-1 |

|--------------------------------------------------------|-----|

| 7.2 Time Base Counter (TBC) Configuration              | 7-1 |

| 7.3 Time Base Counter Registers                        | 7-2 |

| 7.4 1/n Counter                                        | 7-2 |

| 7.4.1 Description of 1/n Counter Registers             | 7-2 |

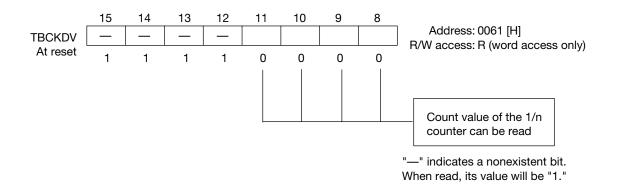

| (1) TBC clock dividing counter (TBCKDV upper 8 bits)   | 7-2 |

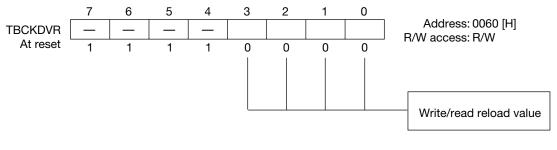

| (2) TBC clock divider register (TBCKDVR)               | 7-3 |

| 7.4.2 Example of 1/n Counter-related Register Settings | 7-4 |

| 7.5 Time Base Counter (TBC) Operation                  | 7-4 |

#### Chapter 8 General-Purpose 8/16 Bit Timers

| 8.1 | Ove | erview                                                   | 8-1 |

|-----|-----|----------------------------------------------------------|-----|

| 8.2 | Ger | neral-purpose 8-bit/16-bit Timer Configurations          | 8-1 |

| 8.3 | Ger | neral-purpose 8-bit/16-bit Timer Registers               | 8-2 |

| 8.4 | Tim | er 0                                                     | 8-3 |

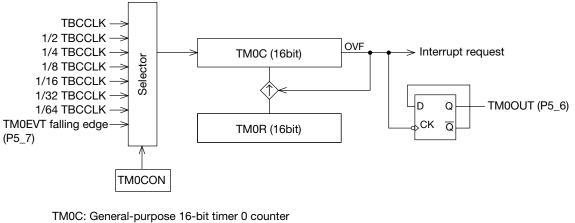

| 8.  | 4.1 | Timer 0 Configuration                                    | 8-3 |

| 8.  | 4.2 | Description of Timer 0 Registers                         | 8-4 |

|     | (1) | General-purpose 16-bit timer 0 counter (TM0C)            |     |

|     | (2) | General-purpose 16-bit timer 0 register (TM0R)           |     |

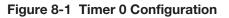

|     | (3) | General-purpose 16-bit timer 0 control register (TM0CON) |     |

| 8.  | 4.3 | Example of Timer 0-related Register Settings             | 8-6 |

|     | (1) | Port 5 mode register (P5IO)                              |     |

|     | (2) | Port 5 secondary function control register (P5SF)        |     |

|     | (3) | General-purpose 16-bit timer 0 counter (TM0C)            | 8-6 |

|     | (4) | General-purpose 16-bit timer 0 register (TM0R)           | 8-6 |

|     | (5) | General-purpose 16-bit timer 0 control register (TM0CON) |     |

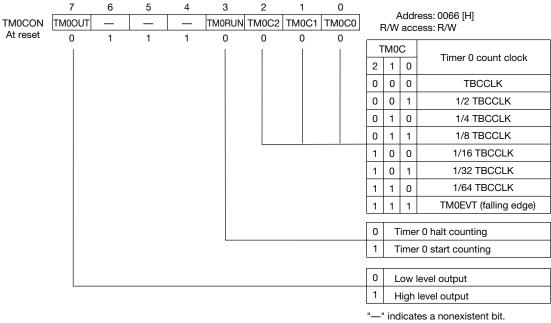

| 8.  | 4.4 | Timer 0 Operation                                        |     |

| 8.  | 4.5 | Timer 0 Interrupt                                        |     |

| 8.5 | Tim | ers 1 and 2                                              |     |

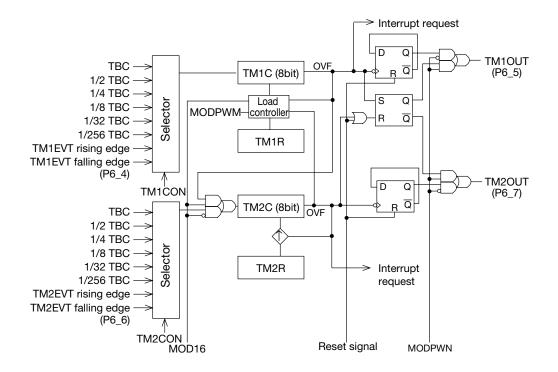

| 8.  | 5.1 | Timers 1 and 2 Configurations                            | 8-9 |

| 8.5.2 | Description of Timer 1 and 2 Registers                     | 8-10 |

|-------|------------------------------------------------------------|------|

| (1)   | General-purpose 8-bit timer 1 and 2 counters (TM1C, TM2C)  | 8-10 |

| (2)   | General-purpose 8-bit timer 1 and 2 registers (TM1R, TM2R) |      |

| (3)   | General-purpose 8-bit timer 1 control register (TM1CON)    |      |

| (4)   | General-purpose 8-bit timer 2 control register (TM2CON)    | 8-11 |

| 8.5.3 | Example of Timer 1- and 2-related Register Settings        | 8-13 |

| •     | 8-bit auto-reload timer mode (Timer 1)                     | 8-13 |

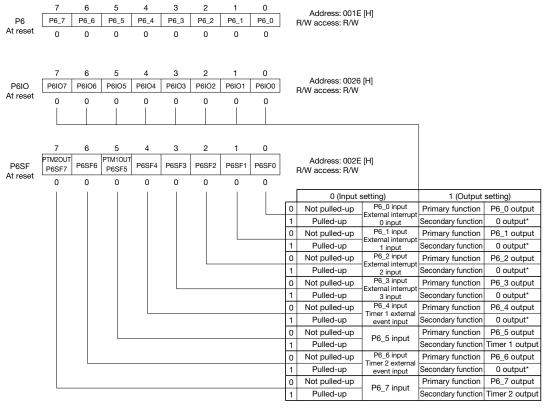

| (1)   | Port 6 mode register (P6IO)                                |      |

| (2)   | Port 6 secondary function control register (P6SF)          | 8-13 |

| (3)   | General-purpose 8-bit timer 1 counter (TM1C)               | 8-13 |

| (4)   | General-purpose 8-bit timer 1 register (TM1R)              | 8-13 |

| (5)   | General-purpose 8-bit timer 1 control register (TM1CON)    | 8-13 |

| •     | 8-bit auto-reload timer mode (Timer 2)                     | 8-13 |

| (1)   | Port 6 mode register (P6IO)                                | 8-13 |

| (2)   | Port 6 secondary function control register (P6SF)          | 8-13 |

| (3)   | General-purpose 8-bit timer 2 counter (TM2C)               | 8-13 |

| (4)   | General-purpose 8-bit timer 2 register (TM2R)              | 8-14 |

| (5)   | General-purpose 8-bit timer 2 control register (TM2CON)    | 8-14 |

| •     | 16-bit auto-reload timer mode                              | 8-14 |

| (1)   | Port 6 mode register (P6IO)                                |      |

| (2)   | Port 6 secondary function control register (P6SF)          | 8-14 |

| (3)   | General-purpose 16-bit timer 12 counter (TM12C)            | 8-14 |

| (4)   | General-purpose 16-bit timer 12 register (TM12R)           | 8-14 |

| (5)   | General-purpose 8-bit timer 1 control register (TM1CON)    | 8-14 |

| (6)   | General-purpose 8-bit timer 2 control register (TM2CON)    | 8-14 |

| •     | PWM mode                                                   | 8-15 |

| (1)   | Port 6 mode register (P6IO)                                | 8-15 |

| (2)   | Port 6 secondary function control register (P6SF)          | 8-15 |

| (3)   | General-purpose 16-bit timer 12 counter (TM12C)            | 8-15 |

| (4)   | General-purpose 16-bit timer 12 register (TM12R)           | 8-15 |

| (5)   | General-purpose 8-bit timer 1 control register (TM1CON)    | 8-15 |

| (6)   | General-purpose 8-bit timer 2 control register (TM2CON)    | 8-15 |

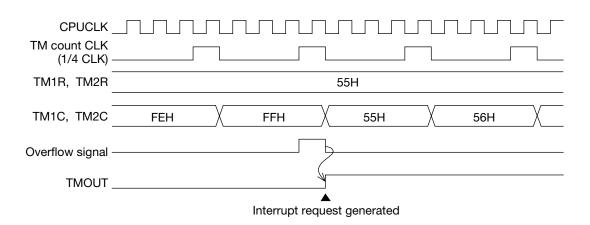

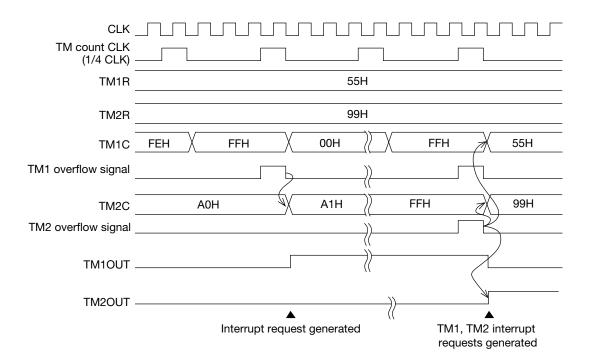

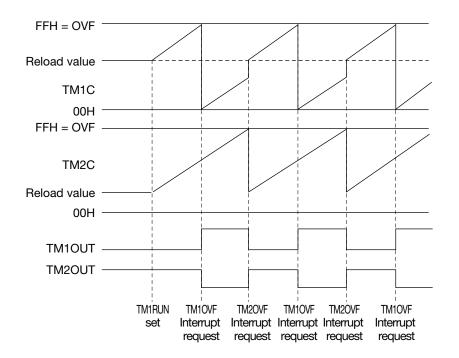

| 8.5.4 | Timer 1 and 2 Operation                                    | 8-16 |

| •     | 8-bit auto-reload timer mode                               | 8-16 |

| •     | 16-bit auto-reload timer mode                              | 8-17 |

| •     | PWM mode                                                   | 8-18 |

| 8.5.5 | Timer 1 and 2 Interrupts                                   | 8-19 |

| •     | Timer 1 interrupt                                          | 8-19 |

| •     | Timer 2 interrupt                                          | 8-20 |

|       |                                                            |      |

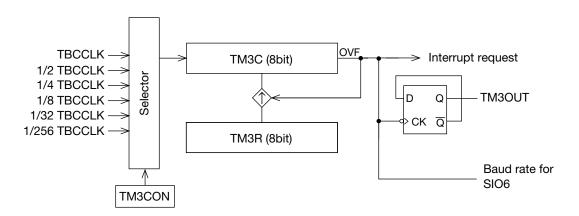

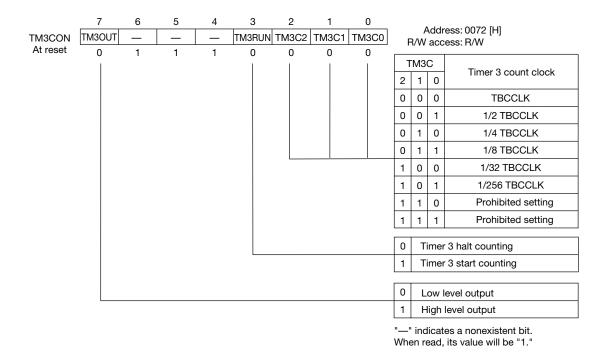

| 8.6 Tim | ner 3                                                   |      |

|---------|---------------------------------------------------------|------|

| 8.6.1   | Timer 3 Configuration                                   | 8-21 |

| 8.6.2   | Description of Timer 3 Registers                        |      |

| (1)     | General-purpose 8-bit timer 3 counter (TM3C)            |      |

| (2)     | General-purpose 8-bit timer 3 register (TM3R)           |      |

| (3)     | General-purpose 8-bit timer 3 control register (TM3CON) |      |

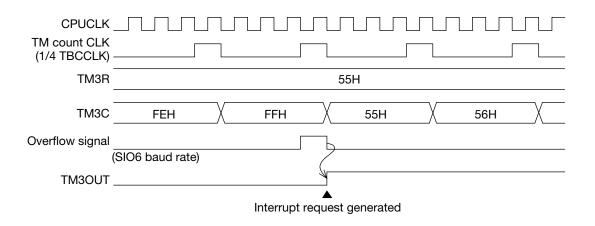

| 8.6.3   | Example of Timer 3-related Register Settings            | 8-24 |

| (1)     | General-purpose 8-bit timer 3 counter (TM3C)            | 8-24 |

| (2)     | General-purpose 8-bit timer 3 register (TM3R)           | 8-24 |

| (3)     | General-purpose 8-bit timer 3 control register (TM3CON) | 8-24 |

| 8.6.4   | Timer 3 Operation                                       | 8-25 |

| 8.6.5   | Timer 3 Interrupt                                       | 8-26 |

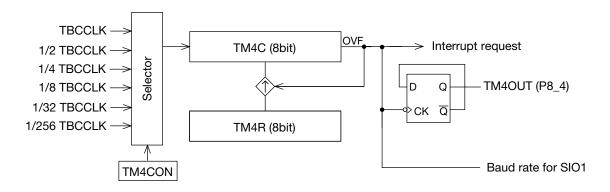

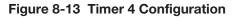

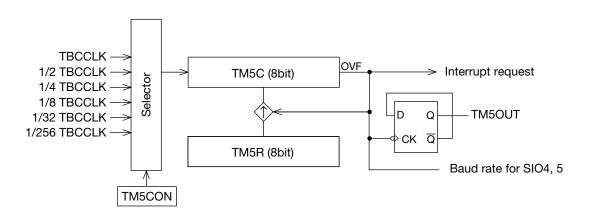

| 8.7 Tim | ner 4                                                   |      |

| 8.7.1   | Timer 4 Configuration                                   |      |

| 8.7.2   | Description of Timer 4 Registers                        | 8-28 |

| (1)     | General-purpose 8-bit timer 4 counter (TM4C)            | 8-28 |

| (2)     | General-purpose 8-bit timer 4 register (TM4R)           | 8-28 |

| (3)     | General-purpose 8-bit timer 4 control register (TM4CON) |      |

| 8.7.3   | Example of Timer 4-related Register Settings            | 8-30 |

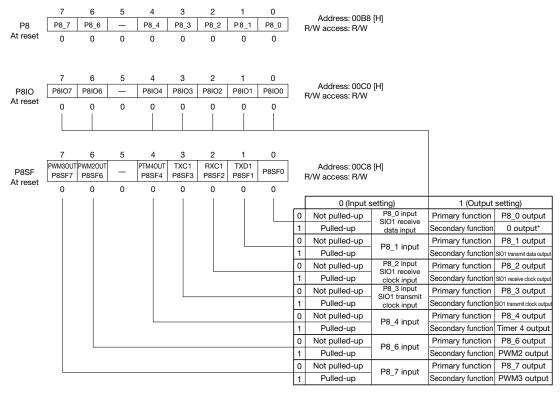

| (1)     | Port 8 mode register (P8IO)                             | 8-30 |

| (2)     | Port 8 secondary function control register (P8SF)       | 8-30 |

| (3)     | General-purpose 8-bit timer 4 counter (TM4C)            |      |

| (4)     | General-purpose 8-bit timer 4 register (TM4R)           |      |

| (5)     | General-purpose 8-bit timer 4 control register (TM4CON) | 8-30 |

| 8.7.4   | Timer 4 Operation                                       | 8-31 |

| 8.7.5   | Timer 4 Interrupt                                       | 8-32 |

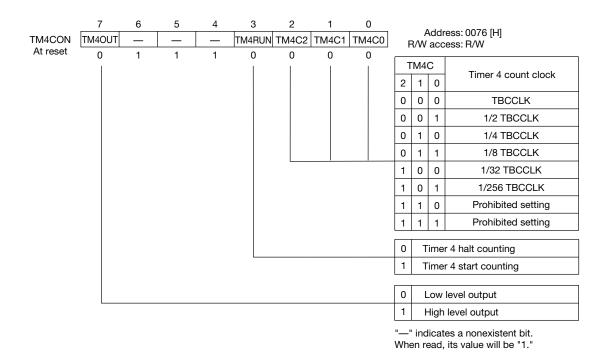

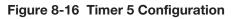

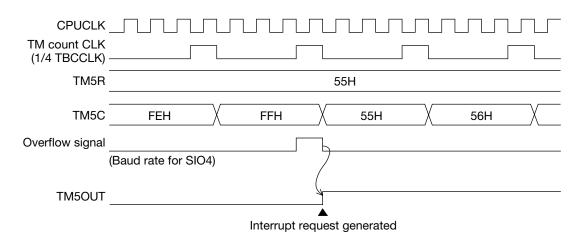

| 8.8 Tim | ner 5                                                   | 8-33 |

| 8.8.1   | Timer 5 Configuration                                   | 8-33 |

| 8.8.2   | Description of Timer 5 Registers                        | 8-34 |

| (1)     | General-purpose 8-bit timer 5 counter (TM5C)            | 8-34 |

| (2)     | General-purpose 8-bit timer 5 register (TM5R)           | 8-34 |

| (3)     | General-purpose 8-bit timer 5 control register (TM5CON) | 8-34 |

| 8.8.3   | Example of Timer 5-related Register Settings            | 8-36 |

| (1)     | General-purpose 8-bit timer 5 counter (TM5C)            |      |

| (2)     | General-purpose 8-bit timer 5 register (TM5R)           | 8-36 |

| (3)     | General-purpose 8-bit timer 5 control register (TM5CON) |      |

| 8.8.4   | Timer 5 Operation                                       |      |

| 8.8.5   | Timer 5 Interrupt                                       |      |

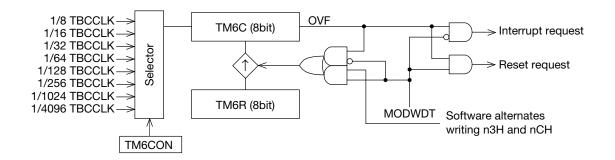

| 8.9 Tim | ner 6                                                   |      |

| 8.9.1   | Timer 6 Configuration                                   | 8-39 |

| 8.9.2    | Description of Timer 6 Registers                        | 8-40 |

|----------|---------------------------------------------------------|------|

| (1)      | General-purpose 8-bit timer 6 counter (TM6C)            | 8-40 |

| (2)      | General-purpose 8-bit timer 6 register (TM6R)           | 8-40 |

| (3)      | General-purpose 8-bit timer 6 control register (TM6CON) | 8-41 |

| 8.9.3    | Example of Timer 6-related Register Settings            | 8-43 |

| •        | Auto-reload timer mode settings                         |      |

| (1)      | General-purpose 8-bit timer 6 counter (TM6C)            | 8-43 |

| (2)      | General-purpose 8-bit timer 6 register (TM6R)           | 8-43 |

| (3)      | General-purpose 8-bit timer 6 control register (TM6CON) | 8-43 |

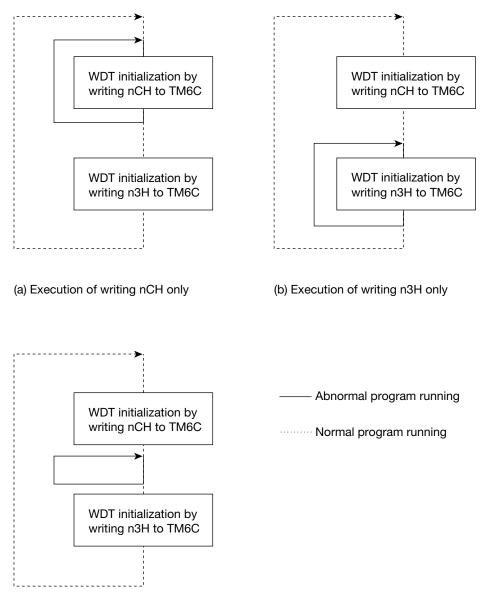

| •        | Watchdog timer (WDT) mode settings                      | 8-43 |

| (1)      | General-purpose 8-bit timer 6 register (TM6R)           | 8-43 |

| (2)      | General-purpose 8-bit timer 6 control register (TM6CON) | 8-43 |

| (3)      | General-purpose 8-bit timer 6 counter (TM6C)            | 8-43 |

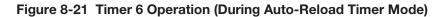

| 8.9.4    | Timer 6 Operation                                       | 8-44 |

| •        | Auto-reload timer mode                                  | 8-44 |

| •        | Watchdog timer (WDT) mode                               | 8-44 |

| 8.9.5    | Timer 6 Interrupt (During Auto-Reload Timer Mode)       | 8-47 |

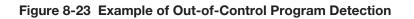

| 8.10 Tin | ner 9                                                   | 8-48 |

| 8.10.1   | Timer 9 Configuration                                   | 8-48 |

| 8.10.2   | Description of Timer 9 Registers                        | 3-49 |

| (1)      | General-purpose 8-bit timer 9 counter (TM9C)            | 8-49 |

| (2)      | General-purpose 8-bit timer 9 register (TM9R)           | 8-49 |

| (3)      | General-purpose 8-bit timer 9 control register (TM9CON) | 8-49 |

| 8.10.3   | Example of Timer 9-related Register Settings            | 8-51 |

| (1)      | General-purpose 8-bit timer 9 counter (TM9C)            | 8-51 |

| (2)      | General-purpose 8-bit timer 9 register (TM9R)           | 8-51 |

| (3)      | General-purpose 8-bit timer 9 control register (TM9CON) | 8-51 |

| 8.10.4   | Timer 9 Operation                                       | 8-52 |

| 8.10.5   | Timer 9 Interrupt                                       | 8-53 |

#### Chapter 9 Capture/Compare Timer

| 9.1 Ove  | erview                                              | 9-1 |

|----------|-----------------------------------------------------|-----|

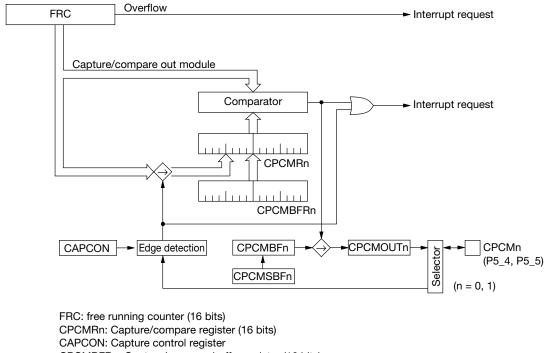

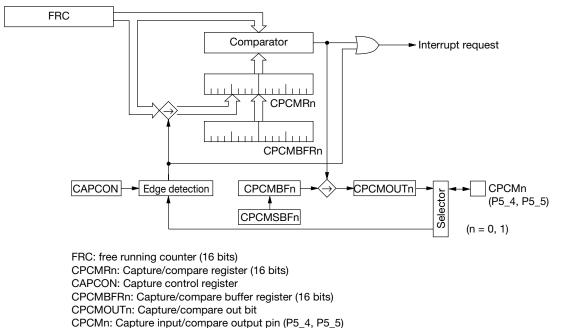

| 9.2 Cap  | oture/Compare Timer Configuration                   | 9-1 |

| 9.3 Cap  | oture/Compare Timer Registers                       | 9-2 |

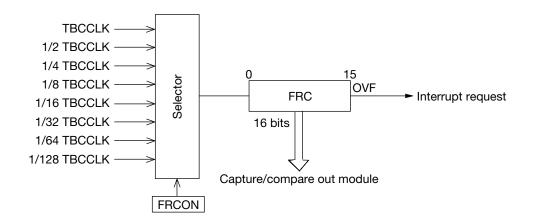

| 9.4 16-l | Bit Free Running Counter (FRC)                      | 9-3 |

| 9.4.1    | 16-Bit Free Running Counter Configuration           | 9-3 |

| 9.4.2    | Description of 16-bit Free Running Counter Register | 9-3 |

| (1)      | 16-bit free running counter (FRC)                   | 9-3 |

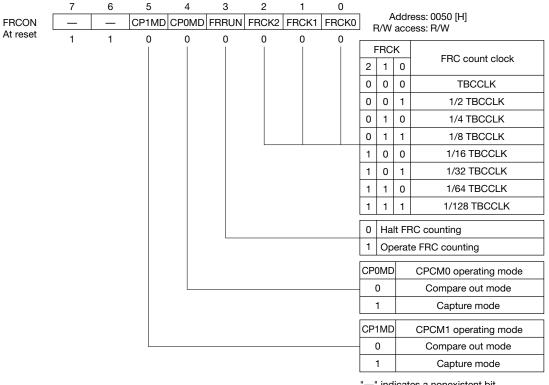

| (2)      | Free running counter control register (FRCON)       | 9-4 |

|          |                                                     |     |

| 9.5 Cap | oture/Compare Out Modules                                  |      |

|---------|------------------------------------------------------------|------|

| 9.5.1   | Capture/Compare Out Module Configuration                   |      |

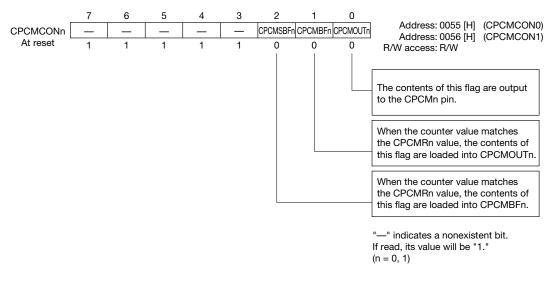

| 9.5.2   | Description of Capture/Compare Out Module Registers        |      |

| (1)     | Capture/compare registers (CPCMR0, CPCMR1)                 |      |

| (2)     | Capture/compare control registers (CPCMCON0, CPCMCON1).    |      |

| (3)     | Capture control register (CAPCON)                          |      |

| (4)     | Capture/compare buffer registers (CPCMBFR0, CPCMBFR1)      |      |

| 9.6 Exa | mple of Capture/Compare Timer-related Register Settings    |      |

| 9.6.1   | Capture Mode Settings                                      |      |

| (1)     | Port 5 mode register (P5IO)                                |      |

| (2)     | Port 5 secondary function control register (P5SF)          |      |

| (3)     | Capture control register (CAPCON)                          |      |

| (4)     | Free running counter (FRC)                                 |      |

| (5)     | Free running counter control register (FRCON)              |      |

| 9.6.2   | Compare Out Mode Settings                                  |      |

| (1)     | Port 5 mode register (P5IO)                                |      |

| (2)     | Port 5 secondary function control register (P5SF)          |      |

| (3)     | Capture/compare control registers (CPCMCON0, CPCMCON1).    |      |

| (4)     | Free running counter (FRC)                                 |      |

| (5)     | Capture/compare registers (CPCMR0, CPCMR1)                 |      |

| (6)     | Capture/compare buffer registers (CPCMBFR0, CPCMBFR1)      |      |

| (7)     | Free running counter control register (FRCON)              |      |

| 9.7 Cap | oture/Compare Timer Operation                              |      |

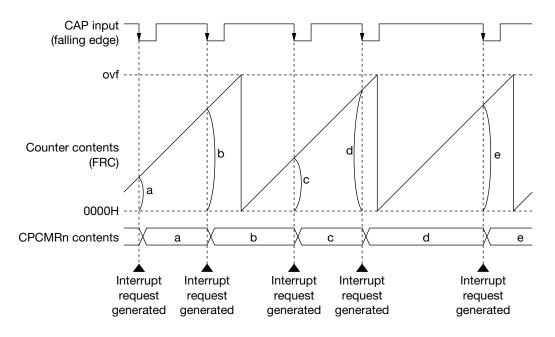

| 9.7.1   | Capture Mode Operation                                     |      |

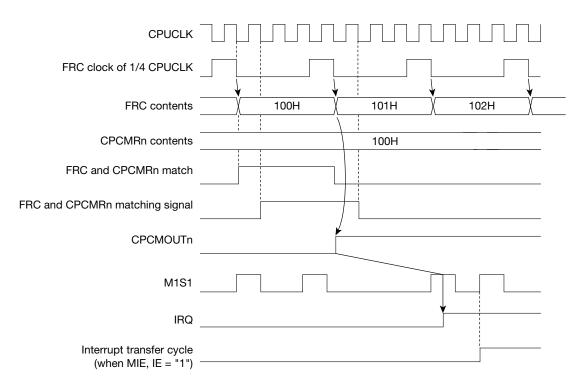

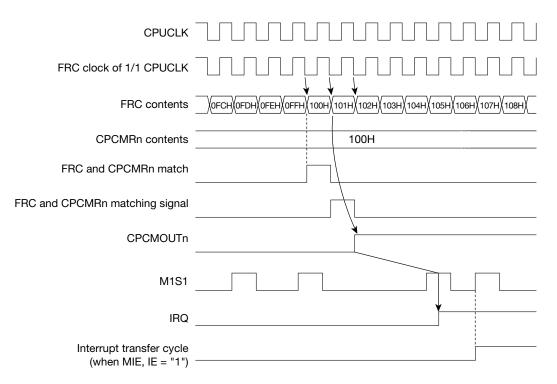

| 9.7.2   | Compare Out Mode Operation                                 | 9-11 |

|         | ample Timings for Changing the Output Level of Compare Out |      |

| 9.9 Cap | oture/Compare Timer Interrupt                              |      |

|         |                                                            |      |

#### Chapter 10 Real-Time Counter (RTC)

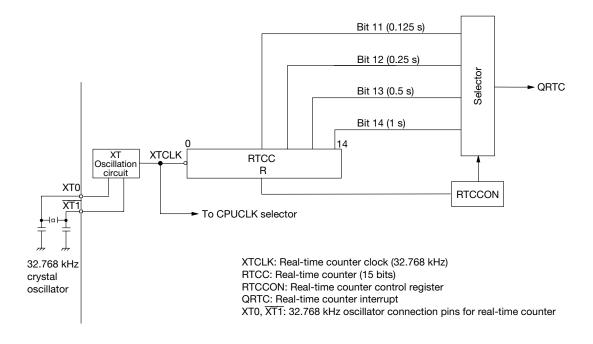

| 10.1 | Overview                                       | 10-1 |

|------|------------------------------------------------|------|

| 10.2 | Real-Time Counter Configuration                | 10-1 |

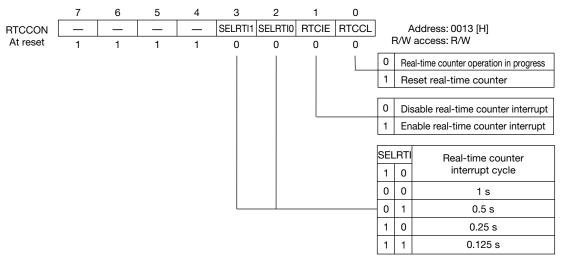

| 10.3 | Real-Time Counter Control Register (RTCCON)    | 10-2 |

| 10.4 | Example of Real-Time Counter Register Settings | 10-3 |

| 10.5 | Real-Time Counter Operation                    | 10-3 |

| 10.6 | Real-Time Counter Interrupt                    | 10-4 |

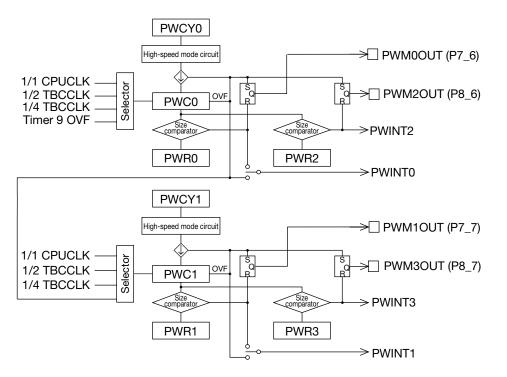

#### Chapter 11 PWM Function

| 11.1 | Overview          | 11 | -1 | 1 |

|------|-------------------|----|----|---|

| 11.2 | PWM Configuration | 11 | -' | 1 |

#### Contents-8

| 11.3 PV | VM Register                                       | 11-2  |

|---------|---------------------------------------------------|-------|

| 11.3.1  | Description of PWM Registers                      | 11-3  |

| (1)     | PWM counters (PWC0, PWC1)                         | 11-3  |

| (2)     | PWM cycle registers (PWCY0, PWCY1)                | 11-3  |

| (3)     | PWM registers (PWR0 to PWR3)                      | 11-4  |

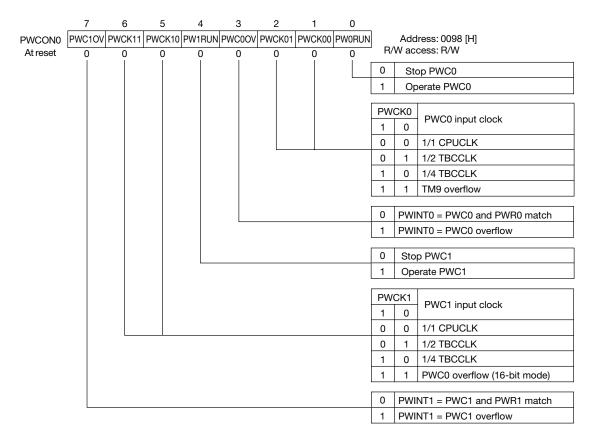

| (4)     | PWM control register 0 (PWCON0)                   | 11-4  |

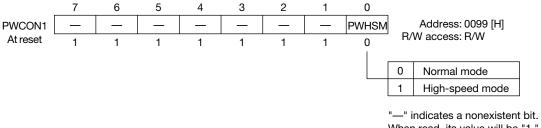

| (5)     | PWM control register 1 (PWCON1)                   | 11-6  |

| 11.3.2  | Example of PWM-related Register Settings          | 11-7  |

| •       | 8-bit PWM settings                                | 11-7  |

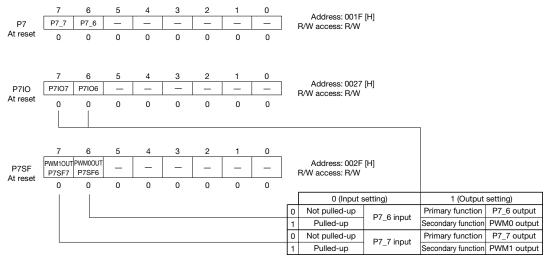

| (1)     | Port 7 mode register (P7IO)                       | 11-7  |

| (2)     | Port 8 mode register (P8IO)                       | 11-7  |

| (3)     | Port 7 secondary function control register (P7SF) | 11-7  |

| (4)     | Port 8 secondary function control register (P8SF) | 11-7  |

| (5)     | PWM counters (PWC0, PWC1)                         | 11-7  |

| (6)     | PWM cycle registers (PWCY0, PWCY1)                | 11-7  |

| (7)     | PWM registers (PWR0 to PWR3)                      | 11-7  |

| (8)     | PWM control register 0 (PWCON0)                   | 11-8  |

| •       | 16-bit PWM settings                               | 11-8  |

| (1)     | Port 7 mode register (P7IO)                       | 11-8  |

| (2)     | Port 8 mode register (P8IO)                       | 11-8  |

| (3)     | Port 7 secondary function control register (P7SF) | 11-8  |

| (4)     | Port 8 secondary function control register (P8SF) | 11-8  |

| (5)     | PWM counters (PWC0, PWC1)                         | 11-8  |

| (6)     | PWM cycle register (PWCY)                         | 11-8  |

| (7)     | PWM registers (PWR01, PWR23)                      | 11-8  |

| (8)     | PWM control register 0 (PWCON0)                   | 11-9  |

| (9)     | PWM control register 1 (PWCON1)                   | 11-9  |

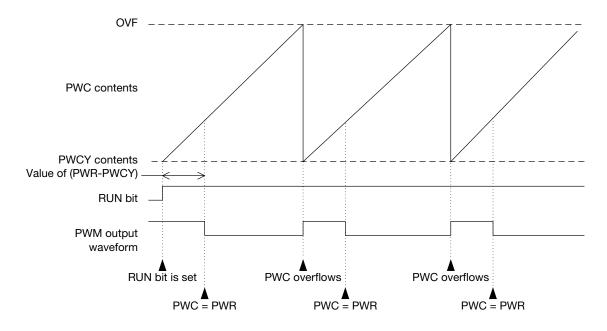

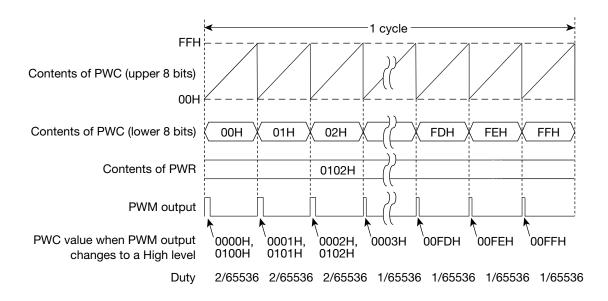

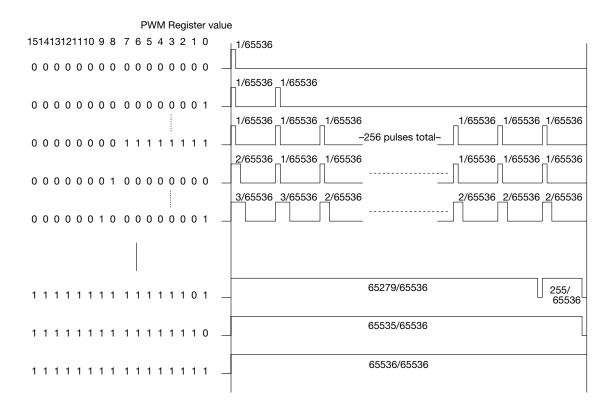

| 11.4 PV | VM Operation                                      | 11-9  |

| 11.4.1  | PWM Operation During 8-bit Mode                   | 11-9  |

| 11.4.2  | PWM Operation During 16-bit Mode                  | 11-10 |

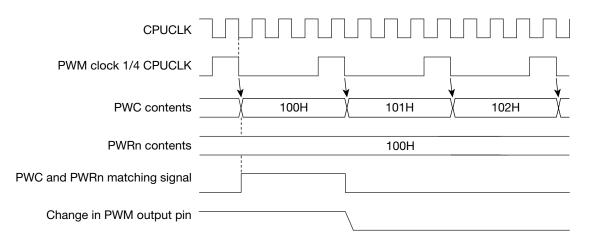

| 11.4.3  | PWM Operation During High-Speed Mode              | 11-12 |

| 11.5 PV | VM Interrupts                                     | 11-14 |

#### Chapter 12 Serial Port Functions

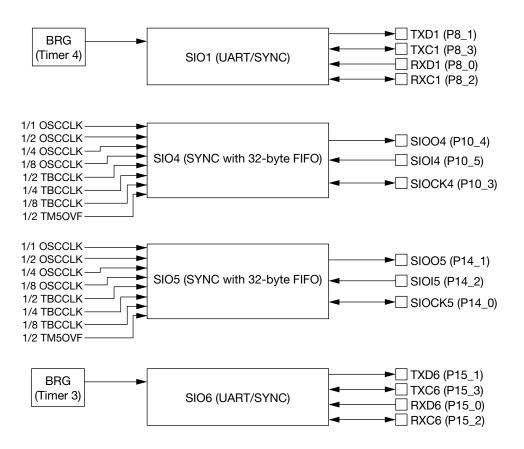

| 12.1 Overview                  |  |

|--------------------------------|--|

| 12.2 Serial Port Configuration |  |

| 12.3 Serial Port Registers     |  |

| 12.4 SIO1                      |  |

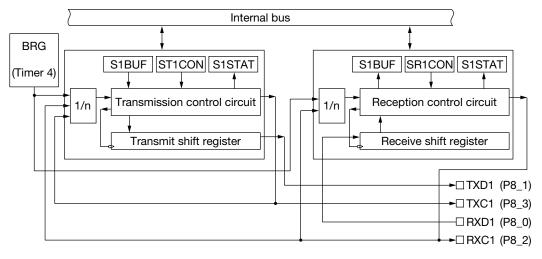

| 12.4.1 SIO1 Configuration      |  |

| 12.4.2  | Description of SIO1 Registers                           | 12-4  |

|---------|---------------------------------------------------------|-------|

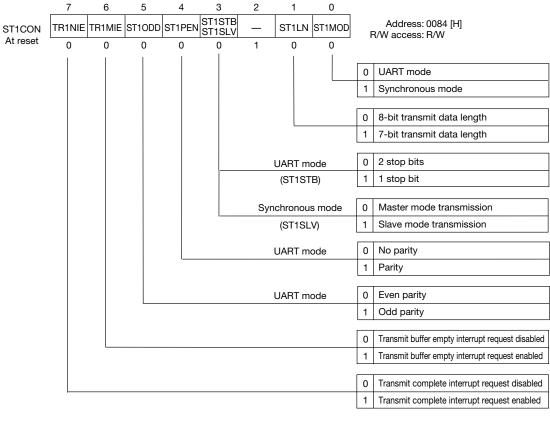

| (1)     | SIO1 transmit control register (ST1CON)                 | 12-4  |

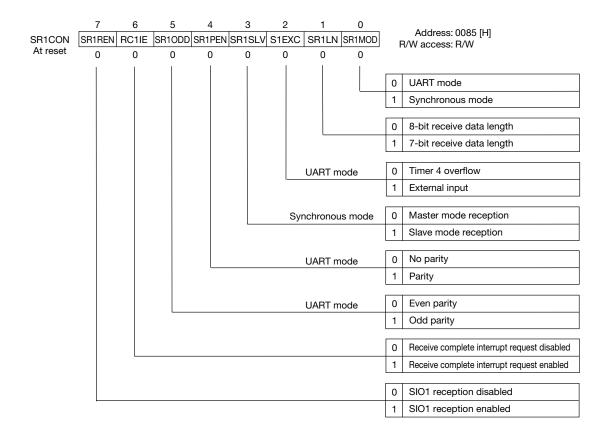

| (2)     | SIO1 receive control register (SR1CON)                  | 12-6  |

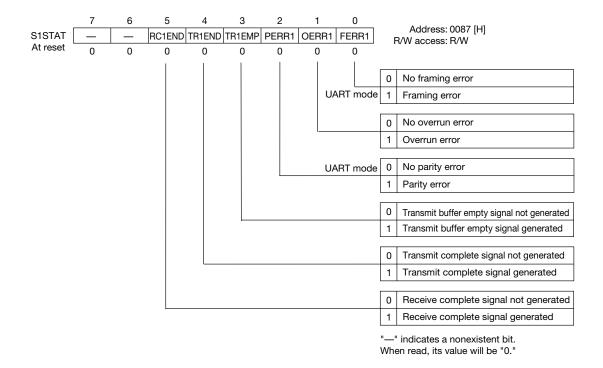

| (3)     | SIO1 status register (S1STAT)                           | 12-8  |

| (4)     | SIO1 transmit-receive buffer register (S1BUF)           | 12-10 |

| (5)     | SIO1 transmit shift register, receive shift register    | 12-10 |

| 12.4.3  | Example of SIO1-related Register Settings               | 12-11 |

| 12.     | 4.3.1 UART Mode Settings                                | 12-11 |

| •       | Transmit settings                                       | 12-11 |

| (1)     | Port 8 mode register (P8IO)                             | 12-11 |

| (2)     | Port 8 secondary function control register (P8SF)       | 12-11 |

| (3)     | SIO1 transmit control register (ST1CON)                 | 12-11 |

| (4)     | SIO1 receive control register (SR1CON)                  | 12-11 |

| (5)     | SIO1 transmit-receive buffer register (S1BUF)           | 12-11 |

| •       | Receive settings                                        | 12-11 |

| (1)     | Port 8 mode register (P8IO)                             | 12-11 |

| (2)     | Port 8 secondary function control register (P8SF)       | 12-11 |

| (3)     | SIO1 receive control register (SR1CON)                  | 12-12 |

| 12.     | 4.3.2 Synchronous Mode Settings                         | 12-12 |

| •       | Transmit settings                                       | 12-12 |

| (1)     | Port 8 mode register (P8IO)                             | 12-12 |

| (2)     | Port 8 secondary function control register (P8SF)       | 12-12 |

| (3)     | SIO1 transmit control register (ST1CON)                 | 12-12 |

| (4)     | SIO1 transmit-receive buffer register (S1BUF)           | 12-12 |

| •       | Receive settings                                        | 12-13 |

| (1)     | Port 8 mode register (P8IO)                             | 12-13 |

| (2)     | Port 8 secondary function control register (P8SF)       | 12-13 |

| (3)     | SIO1 receive control register (SR1CON)                  | 12-13 |

| 12.     | 4.3.3 Baud Rate Generator (Timer 4) Settings            | 12-13 |

| (1)     | General-purpose 8-bit timer 4 counter (TM4C)            | 12-13 |

| (2)     | General-purpose 8-bit timer 4 control register (TM4CON) | 12-13 |

| 12.4.4  | SIO1 Interrupt                                          | 12-14 |

| 12.5 SI | D6                                                      | 12-15 |

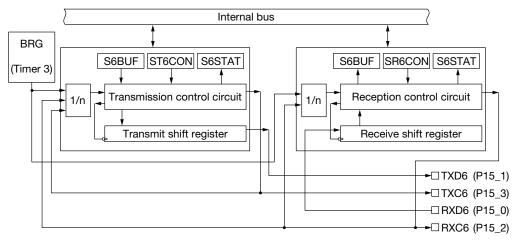

| 12.5.1  | SIO6 Configuration                                      | 12-15 |

| 12.5.2  | Description of SIO6 Registers                           | 12-16 |

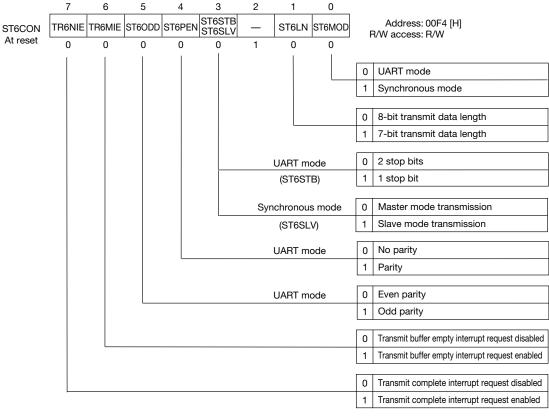

| (1)     | SIO6 transmit control register (ST6CON)                 | 12-16 |

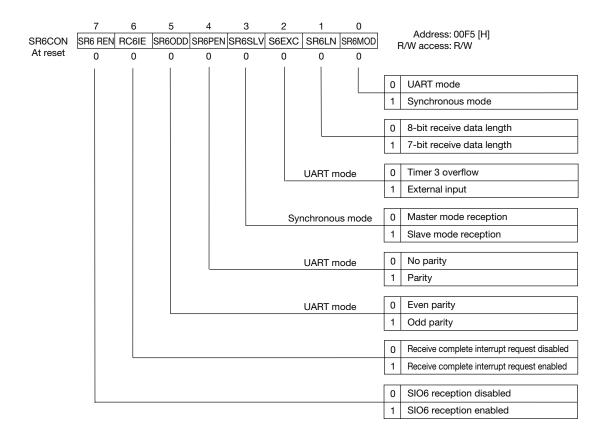

| (2)     | SIO6 receive control register (SR6CON)                  | 12-18 |

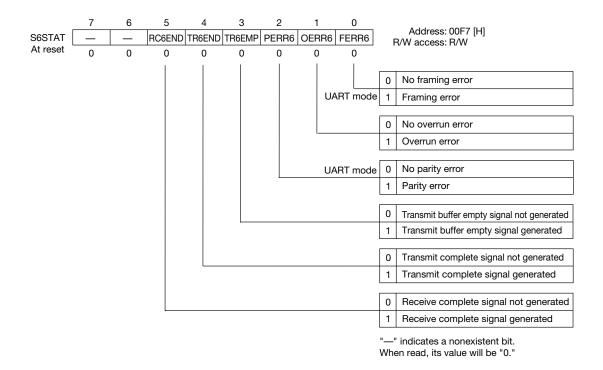

| (3)     | SIO6 status register (S6STAT)                           | 12-20 |

| (4)     | SIO6 transmit-receive buffer register (S6BUF)           | 12-22 |

| (5)     | SIO6 transmit shift register, receive shift register    | 12-22 |

| 12.5.3  | Example of SIO6-related Register Settings               | 12-23 |

|---------|---------------------------------------------------------|-------|

| 12.5    | 5.3.1 UART Mode Settings                                | 12-23 |

| •       | Transmit settings                                       | 12-23 |

| (1)     | Port 15 mode register (P15IO)                           | 12-23 |

| (2)     | Port 15 secondary function control register (P15SF)     | 12-23 |

| (3)     | SIO6 transmit control register (ST6CON)                 | 12-23 |

| (4)     | SIO6 receive control register (SR6CON)                  | 12-23 |

| (5)     | SIO6 transmit-receive buffer register (S6BUF)           | 12-23 |

| •       | Receive settings                                        | 12-23 |

| (1)     | Port 15 mode register (P15IO)                           | 12-23 |

| (2)     | Port 15 secondary function control register (P15SF)     | 12-23 |

| (3)     | SIO6 receive control register (SR6CON)                  | 12-24 |

| 12.     | 5.3.2 Synchronous Mode Settings                         | 12-24 |

| •       | Transmit settings                                       | 12-24 |

| (1)     | Port 15 mode register (P15IO)                           | 12-24 |

| (2)     | Port 15 secondary function control register (P15SF)     | 12-24 |

| (3)     | SIO6 transmit control register (ST6CON)                 | 12-24 |

| (4)     | SIO6 transmit-receive buffer register (S6BUF)           | 12-24 |

| •       | Receive settings                                        | 12-25 |

| (1)     | Port 15 mode register (P15IO)                           | 12-25 |

| (2)     | Port 15 secondary function control register (P15SF)     | 12-25 |

| (3)     | SIO6 receive control register (SR6CON)                  | 12-25 |

| 12.     | 5.3.3 Baud Rate Generator (Timer 3) Settings            | 12-25 |

| (1)     | General-purpose 8-bit timer 3 counter (TM3C)            | 12-25 |

| (2)     | General-purpose 8-bit timer 3 control register (TM3CON) | 12-25 |

| 12.5.4  | SIO6 Interrupt                                          | 12-26 |

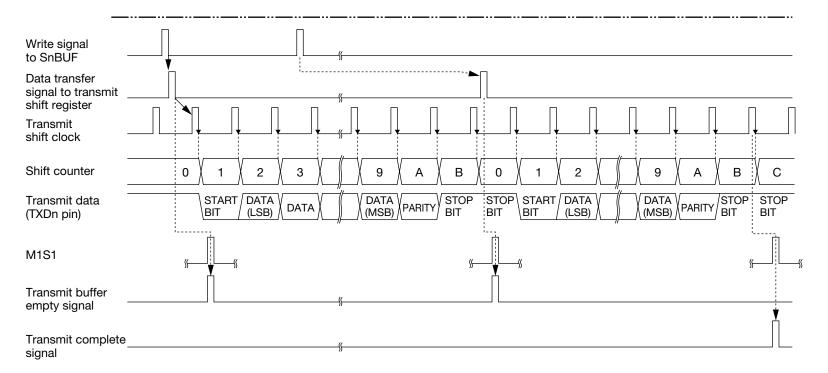

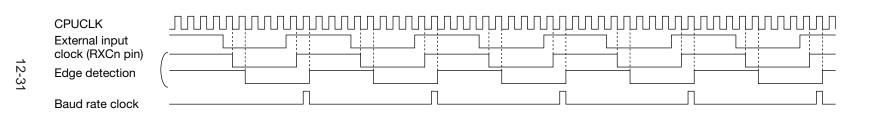

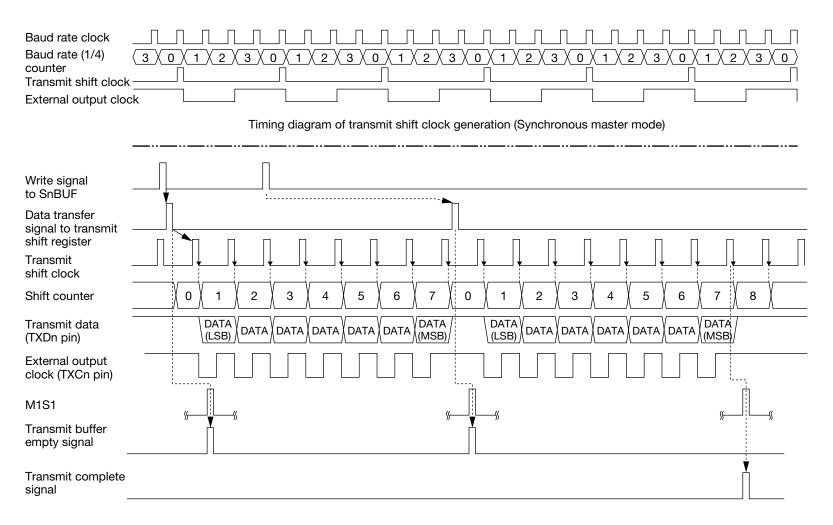

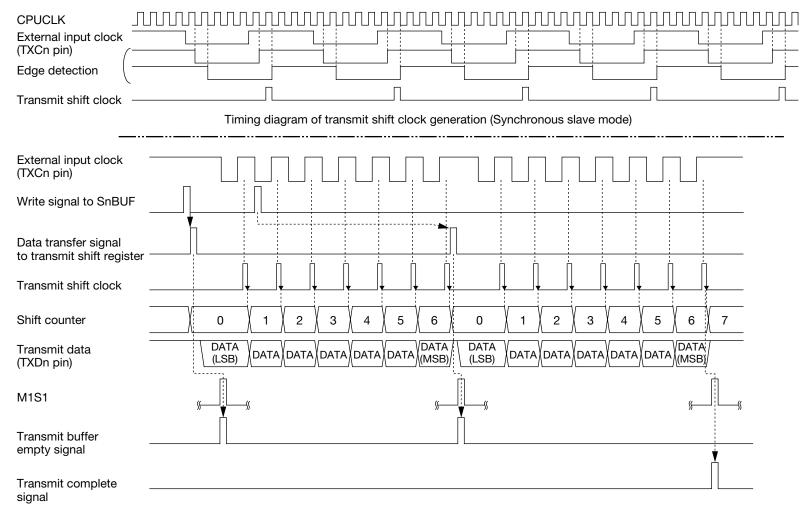

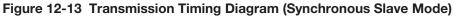

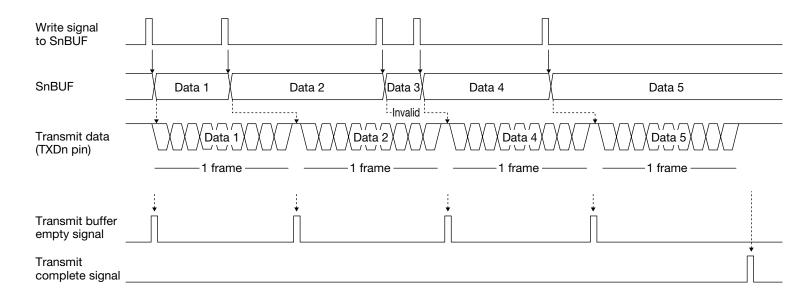

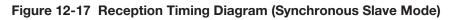

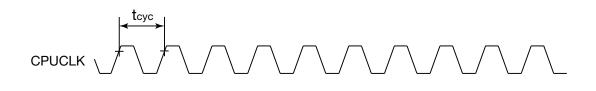

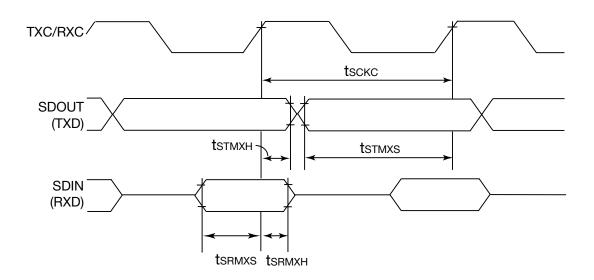

| 12.6 SI | O1, SIO6 Operation                                      | 12-27 |

| 12.6.1  | Transmit Operation                                      | 12-27 |

| •       | UART mode                                               | 12-27 |

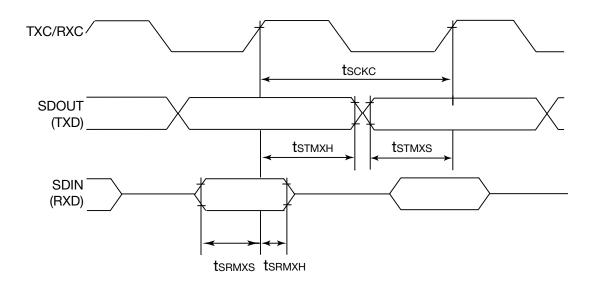

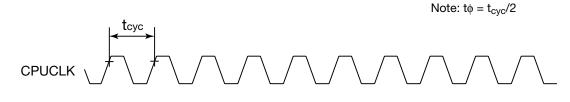

| •       | Synchronous mode                                        | 12-28 |

| 12.6.2  | Receive Operation                                       | 12-35 |

| •       | UART mode                                               | 12-35 |

| •       | Synchronous mode                                        | 12-36 |

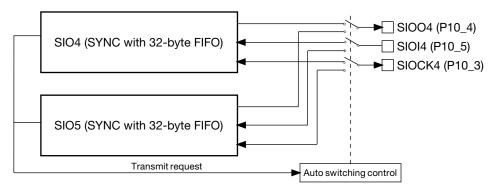

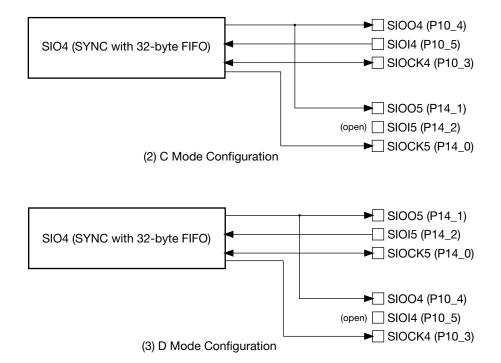

| 12.7 SI | 04                                                      | 12-40 |

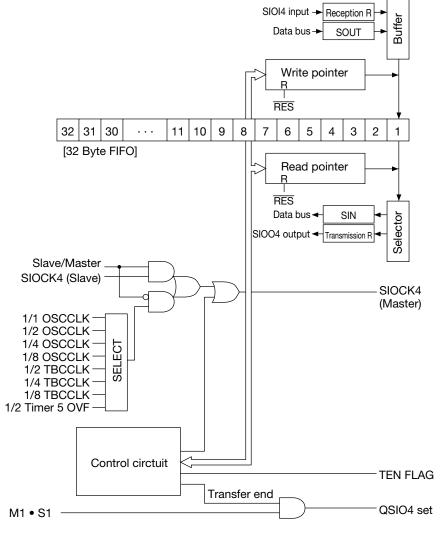

| 12.7.1  | SIO4 Configuration                                      | 12-40 |

| 12.7.2  | Description of SIO4 Registers                           | 12-41 |

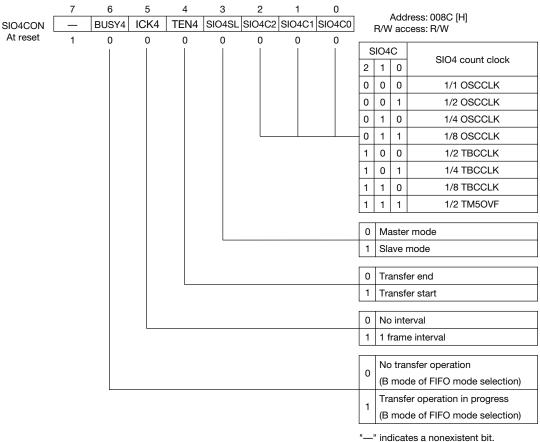

| (1)     | SIO4 control register (SIO4CON)                         | 12-41 |

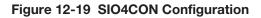

| (2)     | FIFO control register (FIFOCON)                         | 12-43 |

| (3)     | Serial input FIFO data register (SIN4)                  | 12-45 |

| (4)     | Serial output FIFO data register (SOUT4)                | 12-45 |

| B Example of SIO4-related Register Settings         | 12-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Master mode settings                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Port 10 mode register (P10IO)                       | 12-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Port 10 secondary function control register (P10SF) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Serial output FIFO data register (SOUT4)            | 12-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SIO4 control register (SIO4CON)                     | 12-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Slave mode settings                                 | 12-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Port 10 mode register (P10IO)                       | 12-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Port 10 secondary function control register (P10SF) | 12-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Sserial output FIFO data register (SOUT4)           | 12-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SIO4 control register (SIO4CON)                     | 12-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SIO4 Interrupt                                      | 12-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

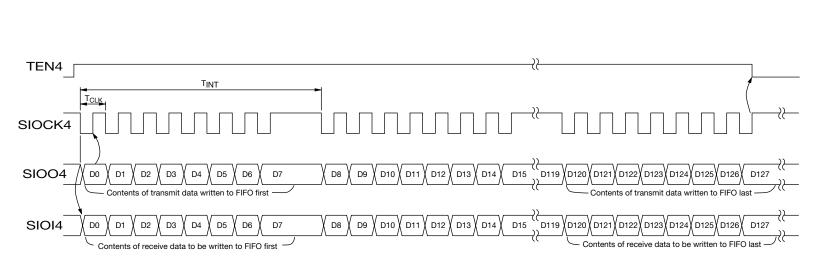

| 5 SIO4 Operation                                    | 12-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

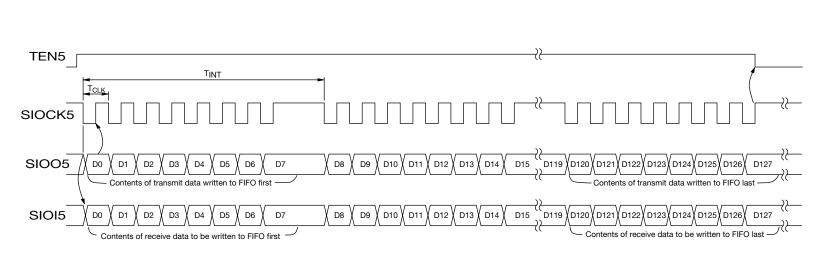

| O5                                                  | 12-51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

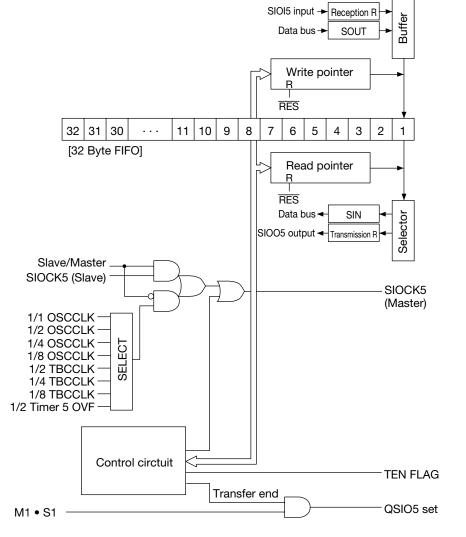

| I SIO5 Configuration                                | 12-51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2 Description of SIO5 Registers                     | 12-52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

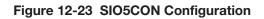

| SIO5 control register (SIO5CON)                     | 12-52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Serial input FIFO data register (SIN5)              | 12-54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Serial output FIFO data register (SOUT5)            | 12-54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FIFO mode control register (FIFOMOD)                | 12-54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Master mode settings                                | 12-57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Port 14 mode register (P14IO)                       | 12-57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Port 14 secondary function control register (P14SF) | 12-57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Serial output FIFO data register (SOUT5)            | 12-57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SIO5 control register (SIO5CON)                     | 12-57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Slave mode settings                                 | 12-58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Port 14 mode register (P14IO)                       | 12-58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Port 14 secondary function control register (P14SF) | 12-58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Serial output FIFO data register (SOUT5)            | 12-58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SIO5 control register (SIO5CON)                     | 12-58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SIO5 Interrupt                                      | 12-59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5 SIO5 Operation                                    | 12-60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                     | Master mode settings<br>Port 10 mode register (P10IO)<br>Port 10 secondary function control register (P10SF)<br>Serial output FIFO data register (SOUT4)<br>SIO4 control register (SIO4CON)<br>Slave mode settings<br>Port 10 mode register (P10IO)<br>Port 10 secondary function control register (P10SF)<br>Sserial output FIFO data register (SOUT4)<br>SIO4 control register (SIO4CON)<br>SIO4 control register (SIO4CON)<br>SIO4 control register (SIO4CON)<br>SIO4 control register (SIO4CON)<br>SIO4 Operation<br>Description of SIO5 Registers<br>SIO5 control register (SIO5CON)<br>Serial input FIFO data register (SIN5) |

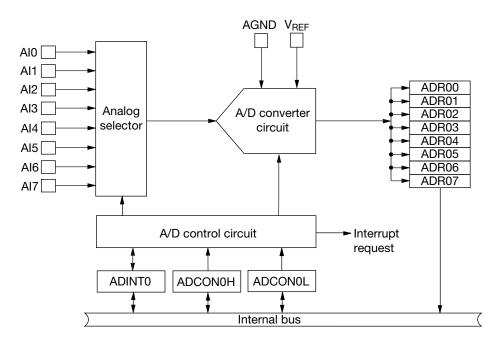

### Chapter 13 A/D Converter Functions

| 13.1 Overview                                 | 13-1 |

|-----------------------------------------------|------|

| 13.2 A/D Converter Configuration              | 13-1 |

| 13.3 A/D Converter Registers                  | 13-2 |

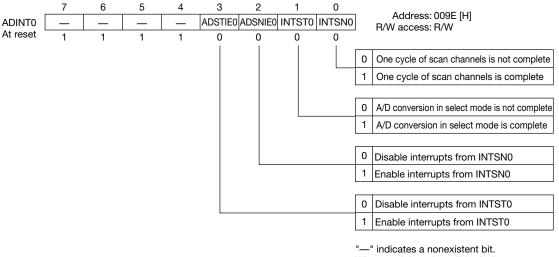

| 13.3.1 Description of A/D Converter Registers | 13-3 |

| (1) A/D control register 0L (ADCON0L)         | 13-3 |

| (2)      | A/D control register 0H (ADCON0H)                  |       |

|----------|----------------------------------------------------|-------|

| (3)      | A/D interrupt control register (ADINT0)            |       |

| (4)      | A/D result registers (ADR00 to ADR07)              |       |

| 13.3.2   | Example of A/D Converter-related Register Settings |       |

| •        | Scan mode setting                                  |       |

| (1)      | A/D control register 0H (ADCON0H)                  |       |

| (2)      | A/D interrupt control register (ADINT0)            |       |

| (3)      | A/D control register 0L (ADCON0L)                  |       |

| •        | Select mode setting                                |       |

| (1)      | A/D interrupt control register (ADINT0)            |       |

| (2)      | A/D control register 0H (ADCON0H)                  |       |

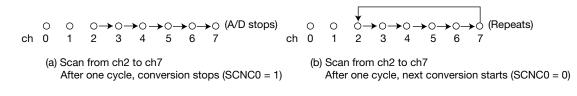

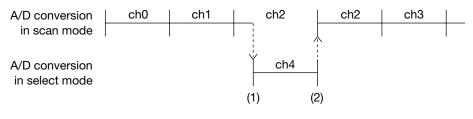

| 13.4 A/I | D Converter Operation                              |       |

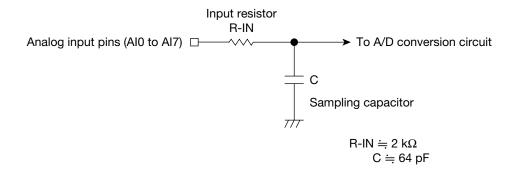

| 13.5 No  | tes Regarding Usage of A/D Converter               |       |

| 13.5.1   | Considerations When Setting the Conversion Time    | 13-11 |

| 13.5.2   | Noise-Suppression Measures                         |       |

| 13.6 A/I | D Converter Interrupt                              |       |

|          |                                                    |       |

#### Chapter 14 D/A Converter Functions

| 14-1 |

|------|

| 14-1 |

| 14-2 |

| 14-2 |

| 14-2 |

| 14-2 |

| 14-3 |

| 14-3 |

| 14-3 |

| 14-3 |

| 14-3 |

| 14-4 |

|      |

#### Chapter 15 Peripheral Functions

| 15.1 Overview                                | 15-1 |

|----------------------------------------------|------|

| 15.2 Description of Each Peripheral Function | 15-1 |

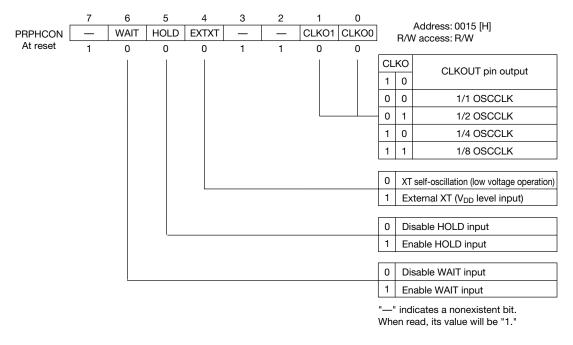

| 15.2.1 Clock Out Function                    |      |

| 15.2.2 External XTCLK Input Control Function | 15-1 |

| 15.2.3 HOLD Input Control Function           |      |

| 15.2.4 WAIT Input Control Function           | 15-1 |

| 15.3 Peripheral Control Register (PRPHCON)   |      |

#### Chapter 16 External Interrupt Functions

| 16.1 Overview                                                  | 16-1 |

|----------------------------------------------------------------|------|

| 16.2 External Interrupt Registers                              | 16-1 |

| 16.2.1 Description of External Interrupt Registers             | 16-2 |

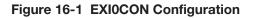

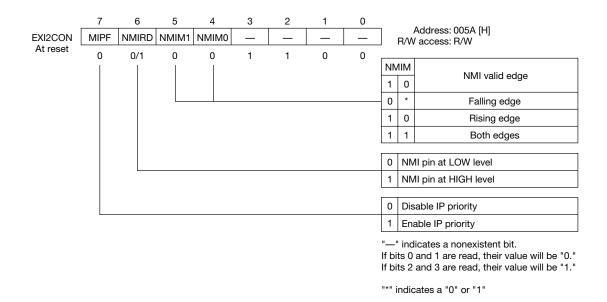

| (1) External interrupt control register 0 (EXI0CON)            | 16-2 |

| (2) External interrupt control register 1 (EXI1CON)            | 16-3 |

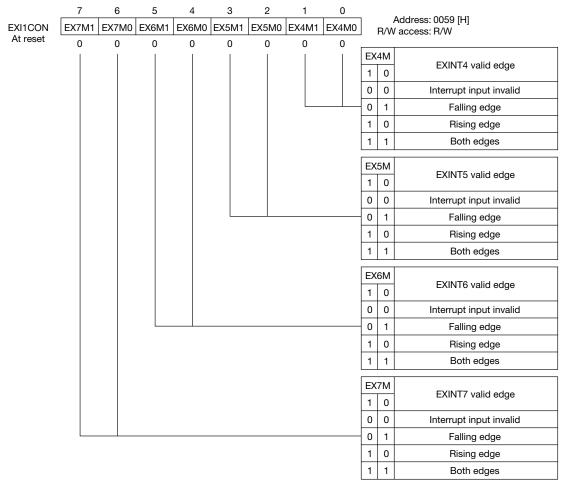

| (3) External interrupt control register 2 (EXI2CON)            | 16-4 |

| 16.2.2 Example of External Interrupt-related Register Settings | 16-5 |

| (1) Port 6 mode register (P6IO)                                | 16-5 |

| (2) Port 9 mode register (P9IO)                                | 16-5 |

| (3) Port 6 secondary function control register (P6SF)          | 16-5 |

| (4) Port 9 secondary function control register (P9SF)          | 16-5 |

| (5) External interrupt control register 0 (EXI0CON)            | 16-5 |

| (6) External interrupt control register 1 (EXI1CON)            | 16-5 |

| (7) External interrupt control register 2 (EXI2CON)            | 16-5 |

| 16.3 EXINT0 to EXINT7 Interrupts                               | 16-6 |

#### Chapter 17 Interrupt Processing Functions

| 17.1 Overview                                                        |

|----------------------------------------------------------------------|

| 17.2 Interrupt Function Registers 17-2                               |

| 17.3 Description of Interrupt Processing17-3                         |

| 17.3.1 Non-Maskable Interrupt (NMI)17-3                              |

| 17.3.2 Maskable Interrupts 17-5                                      |

| (1) Interrupt request registers (IRQ0 to IRQ4)17-5                   |

| (2) Interrupt enable registers (IE0 to IE4)17-5                      |

| (3) Master interrupt enable flag (MIE)17-5                           |

| (4) Master interrupt priority flag (MIPF)17-5                        |

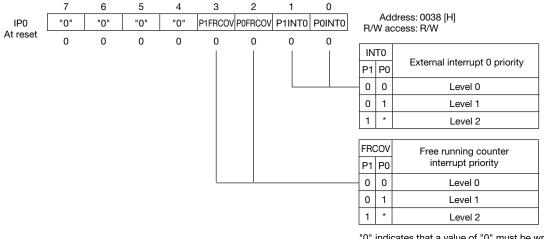

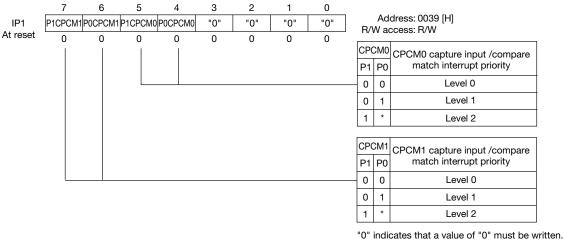

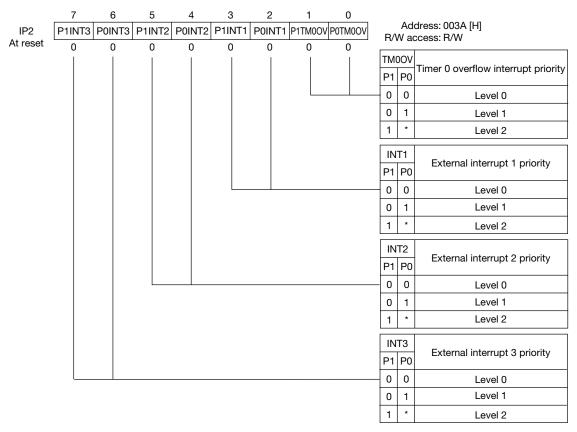

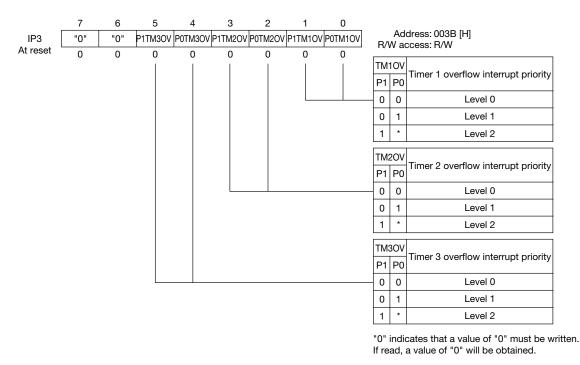

| (5) Interrupt priority control registers (IP0 to IP9) 17-6           |

| 17.3.3 Priority Control of Maskable Interrupts 17-10                 |

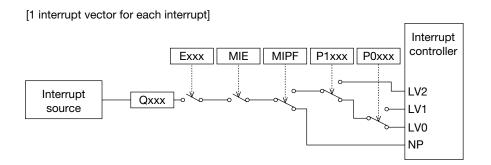

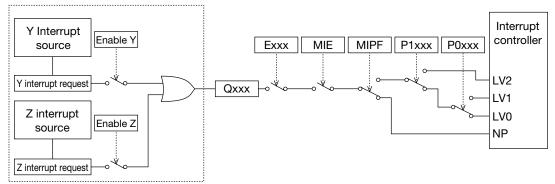

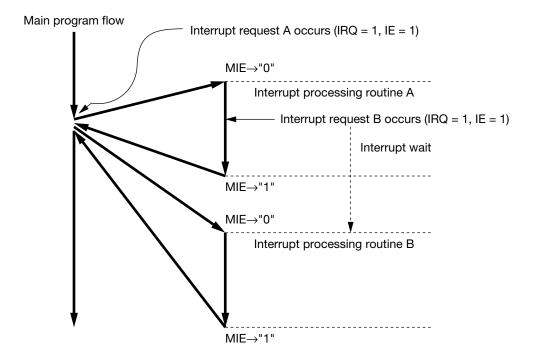

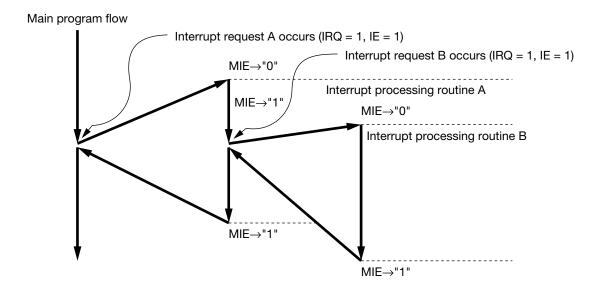

| (1) Basic interrupt control17-10                                     |

| (2) Multiple interrupt control17-10                                  |

| 17.4 IRQ, IE and IP Register Configurations for Each Interrupt 17-12 |

| 17.4.1 Interrupt Request Registers (IRQ0 to IRQ4) 17-12              |

| (1) Interrupt request register 0 (IRQ0)17-12                         |

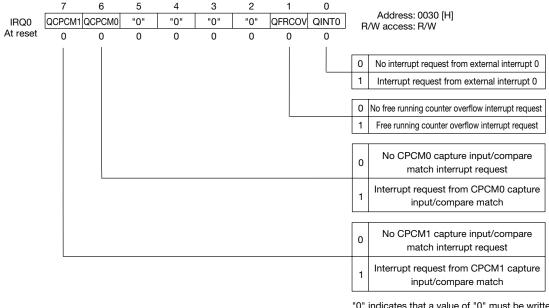

| (2) Interrupt request register 1 (IRQ1) 17-13                        |

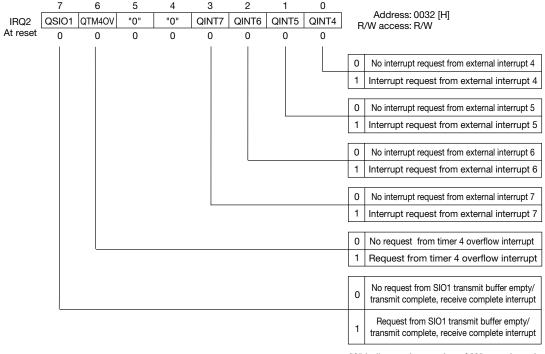

| (3) Interrupt request register 2 (IRQ2)17-14                         |

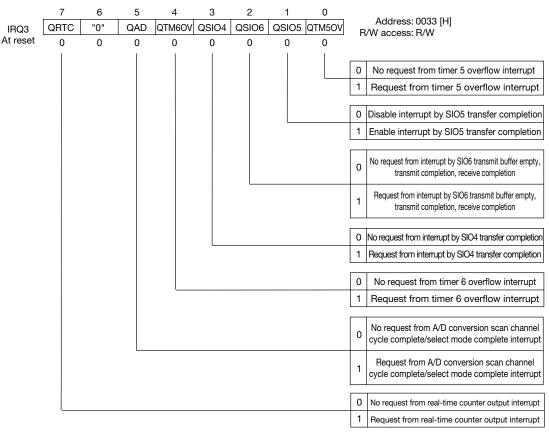

| (4) Interrupt request register 3 (IRQ3)17-15                         |

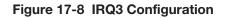

| (5) Interrupt request register 4 (IRQ4) 17-16                        |

| 17.4.2 Interrupt Enable Registers (IE0 to IE4) 17-17                 |

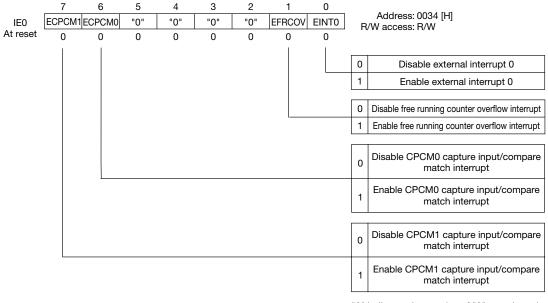

| (1) Interrupt enable register 0 (IE0) 17-17                          |

| (2)    | Interrupt enable register 1 (IE1)                 |       |

|--------|---------------------------------------------------|-------|

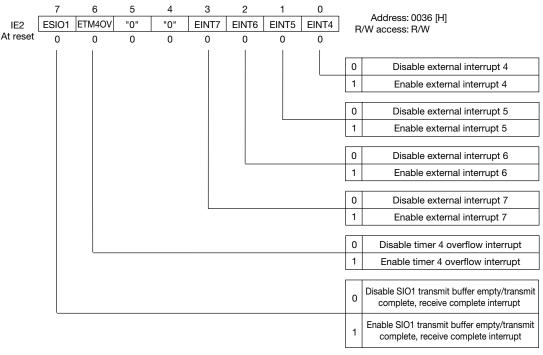

| (3)    | Interrupt enable register 2 (IE2)                 |       |

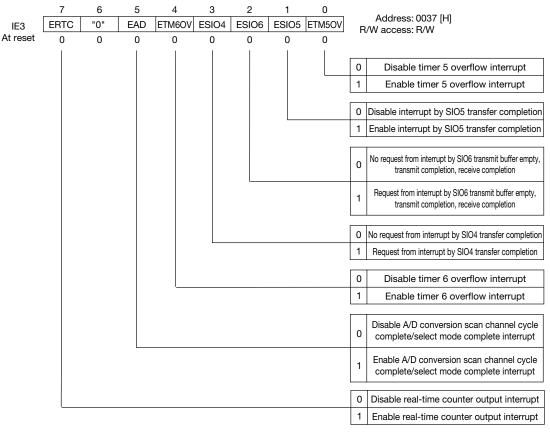

| (4)    | Interrupt enable register 3 (IE3)                 |       |

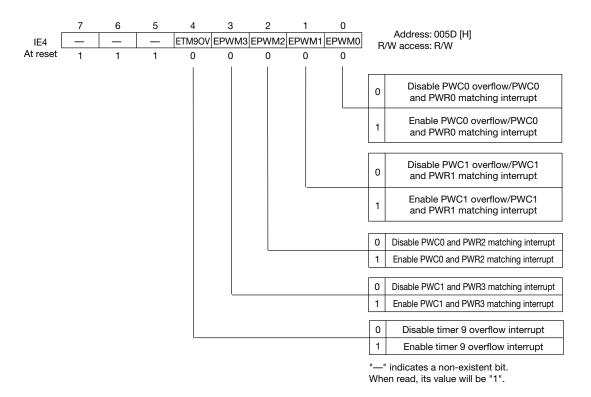

| (5)    | Interrupt enable register 4 (IE4)                 |       |

| 17.4.3 | Interrupt Priority Control Registers (IP0 to IP9) | 17-22 |

| (1)    | Interrupt priority control register 0 (IP0)       |       |

| (2)    | Interrupt priority control register 1 (IP1)       |       |

| (3)    | Interrupt priority control register 2 (IP2)       |       |

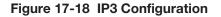

| (4)    | Interrupt priority control register 3 (IP3)       |       |

| (5)    | Interrupt priority control register 4 (IP4)       |       |

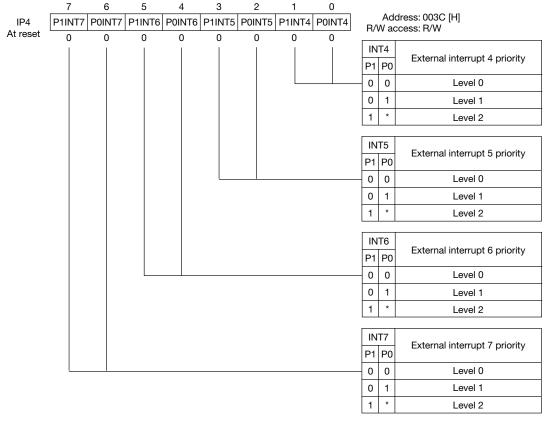

| (6)    | Interrupt priority control register 5 (IP5)       |       |

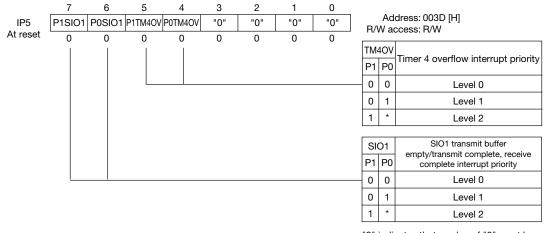

| (7)    | Interrupt priority control register 6 (IP6)       |       |

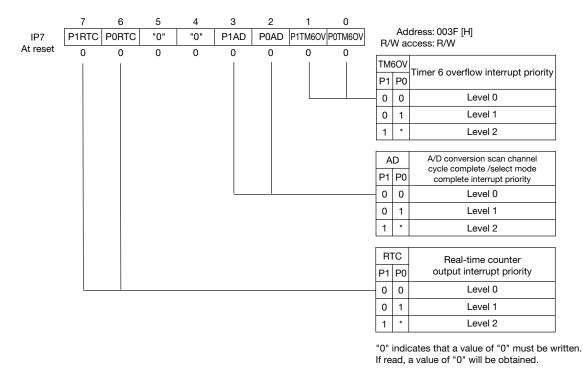

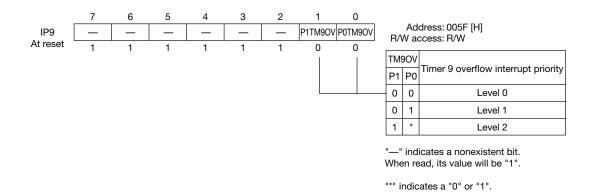

| (8)    | Interrupt priority control register 7 (IP7)       |       |

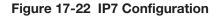

| (9)    | Interrupt priority control register 8 (IP8)       |       |

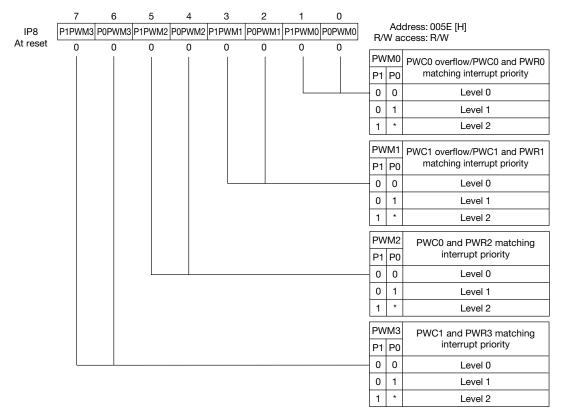

| (10)   | Interrupt priority control register 9 (IP9)       | 17-31 |

|        |                                                   |       |

#### Chapter 18 Bus Port Functions

| 18.1 Overview                                       |  |

|-----------------------------------------------------|--|

| 18.2 Port Operation                                 |  |

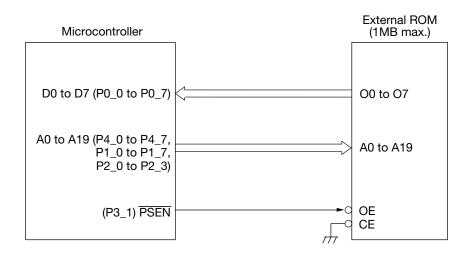

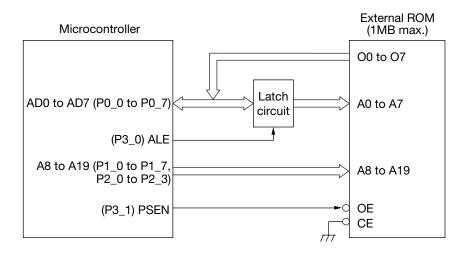

| 18.2.1 Port Operation When Accessing Program Memory |  |

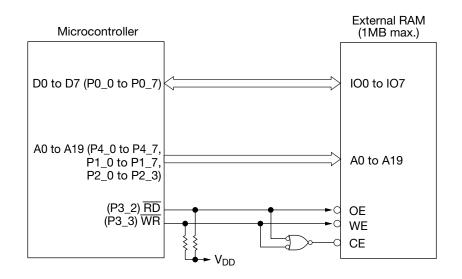

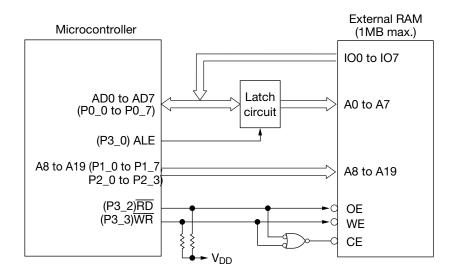

| 18.2.2 Port Operation When Accessing Data Memory    |  |

| 18.3 External Memory Access                         |  |

| 18.3.1 External Program Memory Access               |  |

| 18.3.2 External Data Memory Access                  |  |

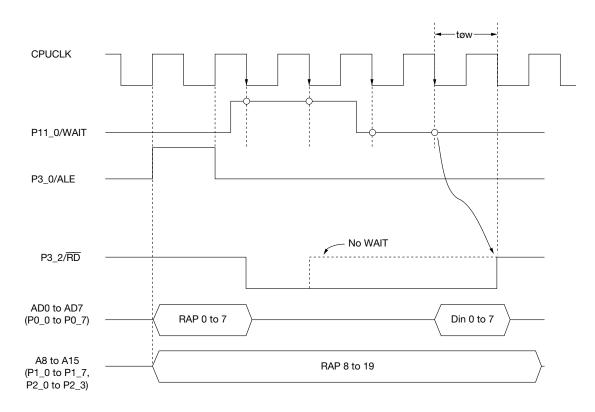

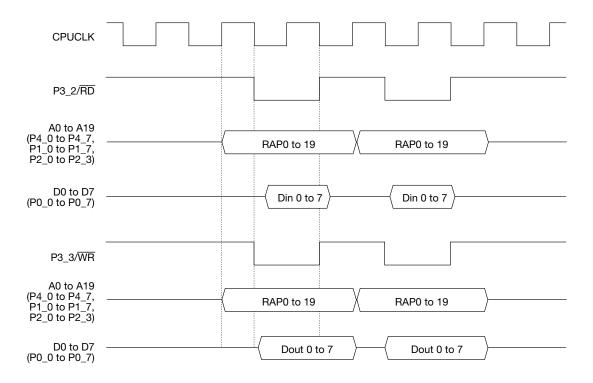

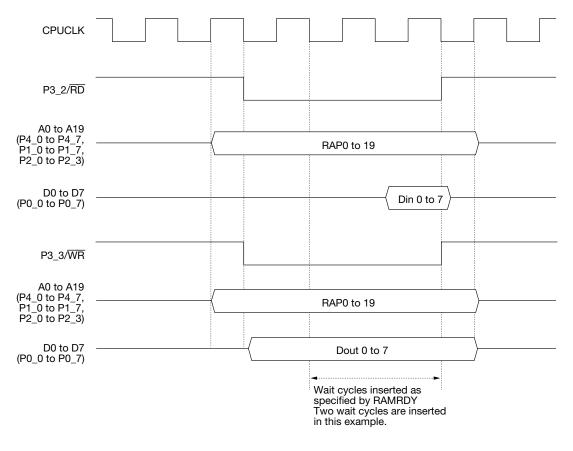

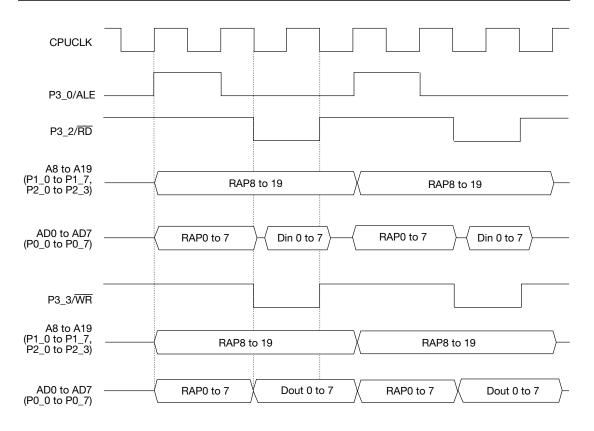

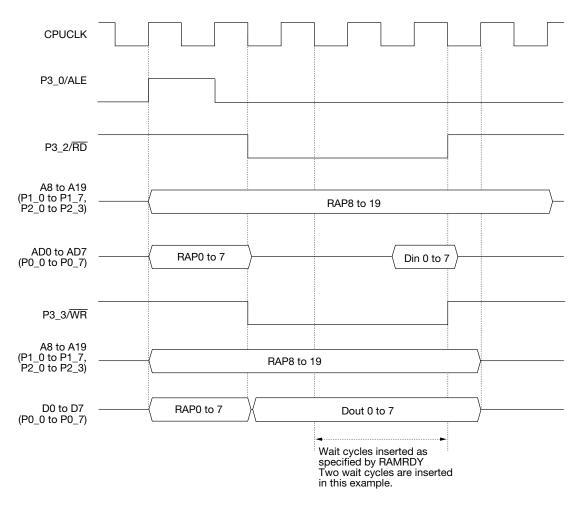

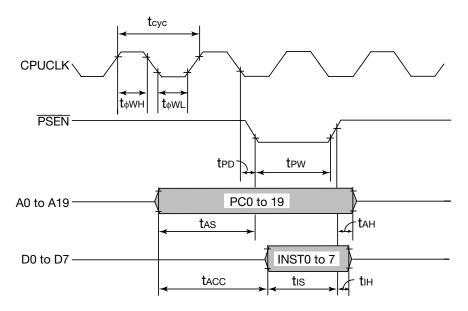

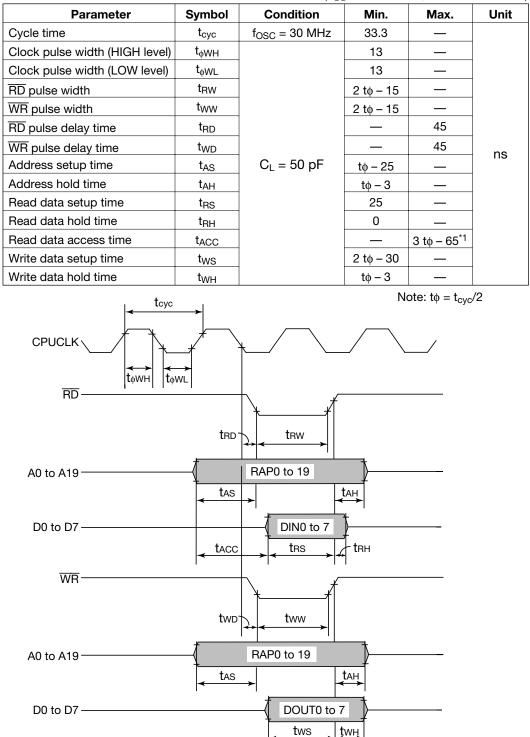

| 18.4 External Memory Access Timing                  |  |

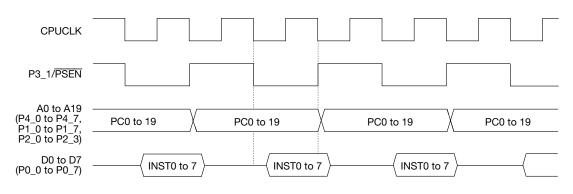

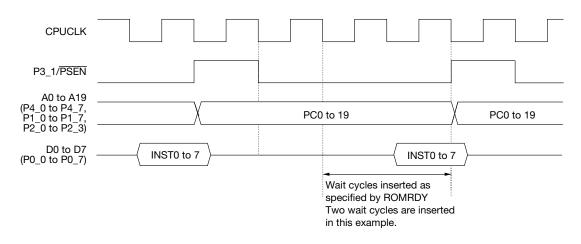

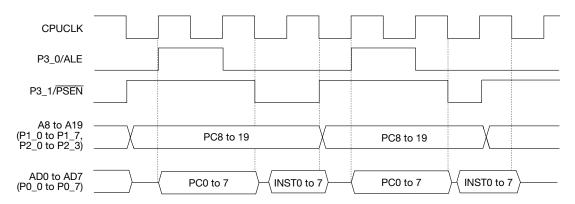

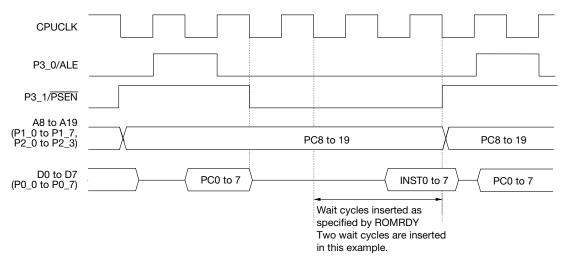

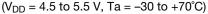

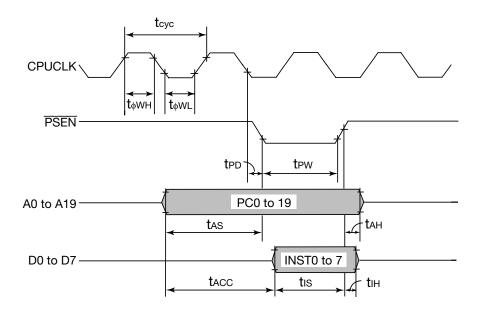

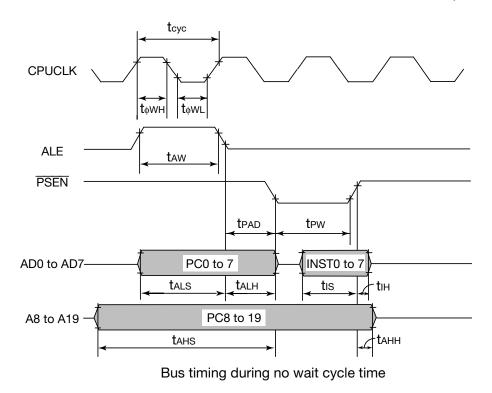

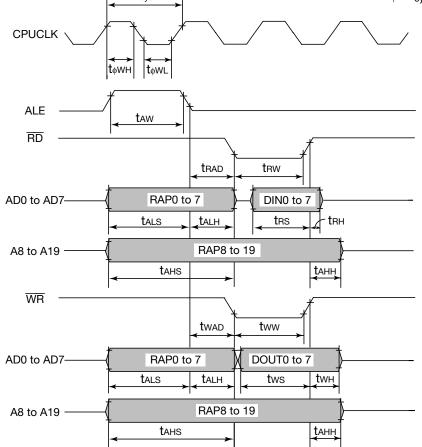

| 18.4.1 External Program Memory Access Timing        |  |

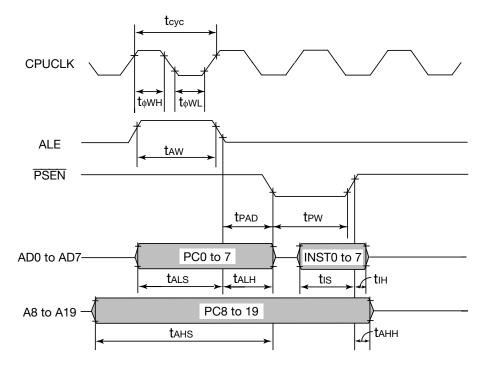

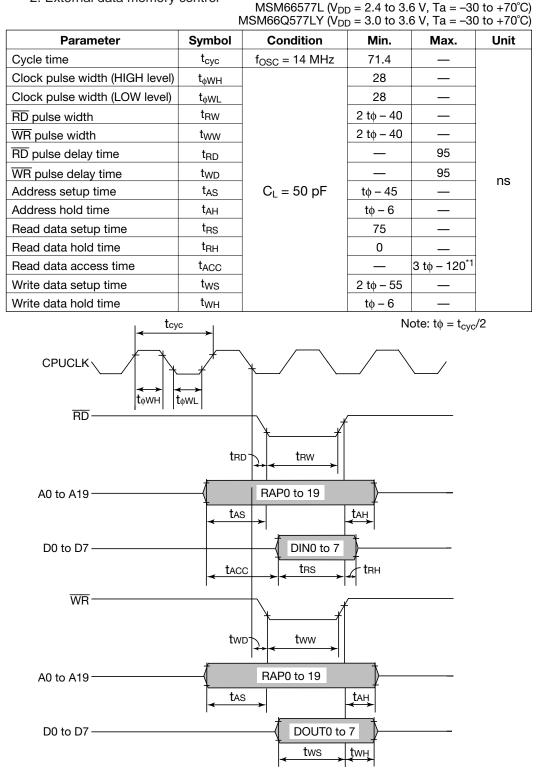

| 18.4.2 External Data Memory Access Timing           |  |

| 18.5 Notes Regarding Usage of Bus Port Function     |  |

| 18.5.1 Dummy Read Strobe Output                     |  |

| 18.5.2 External Bus Access Timing                   |  |

#### Chapter 19 Flash Memory

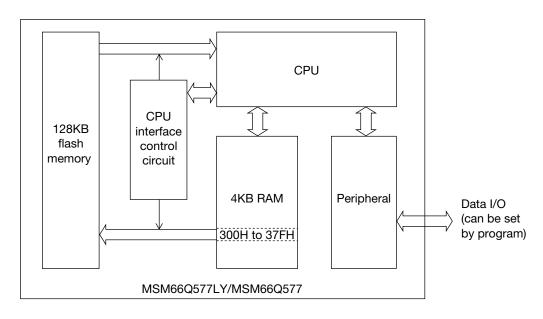

| 19.1 Overview                                      | 19-1 |

|----------------------------------------------------|------|

| 19.2 Features                                      | 19-1 |

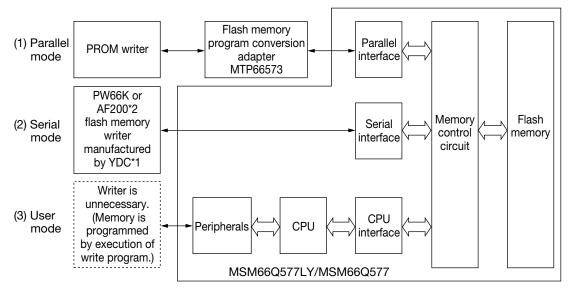

| 19.3 Programming Modes                             | 19-2 |

| 19.4 Parallel Mode                                 | 19-4 |

| 19.4.1 Overview of the Parallel Mode               | 19-4 |

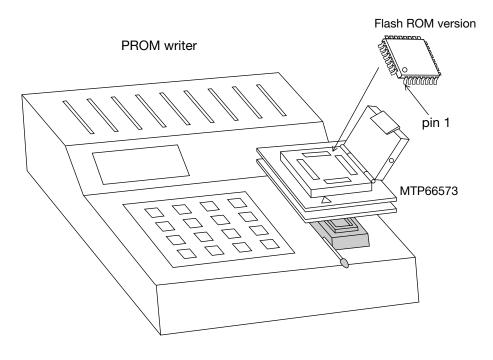

| 19.4.2 PROM Writer Setting                         | 19-4 |

| 19.4.3 Flash Memory Programming Conversion Adapter | 19-4 |

| 19.5 Se | rial Mode                                                |  |

|---------|----------------------------------------------------------|--|

| 19.5.1  | Overview of the Serial Mode                              |  |

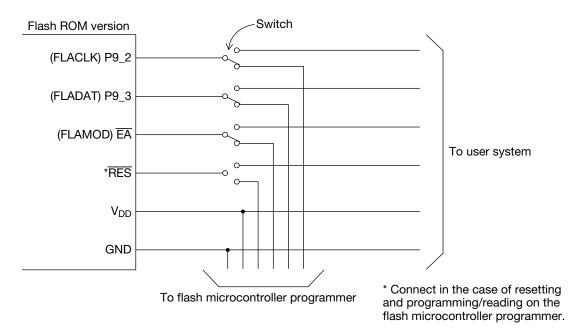

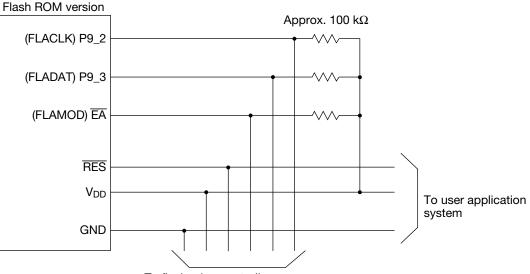

| 19.5.2  | Serial Mode Settings                                     |  |

| (1)     | Pins used in serial mode                                 |  |

| (2)     | Serial mode connection circuit                           |  |

| (3)     | Serial mode programming method                           |  |

| (4)     | Setting of security function                             |  |

| (5)     | Notes on use of serial mode                              |  |

| 19.6 Us | er Mode                                                  |  |

| 19.6.1  | Overview of the User Mode                                |  |

| 19.6.2  | User Mode Programming Registers                          |  |

| 19.6.3  | Description of User Mode Registers                       |  |

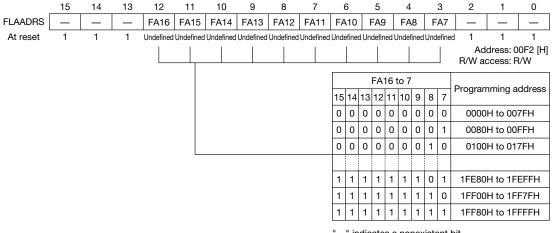

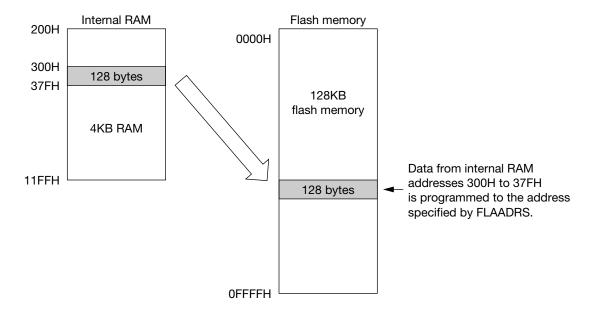

| (1)     | Flash memory address register (FLAADRS)                  |  |

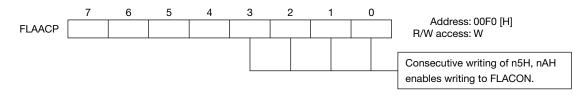

| (2)     | Flash memory acceptor (FLAACP)                           |  |

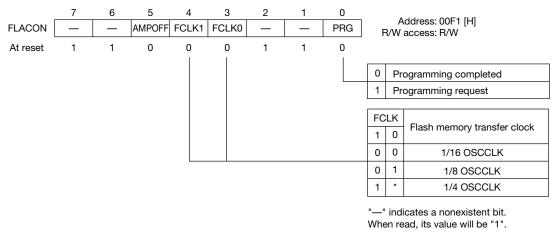

| (3)     | Flash memory control register (FLACON)                   |  |

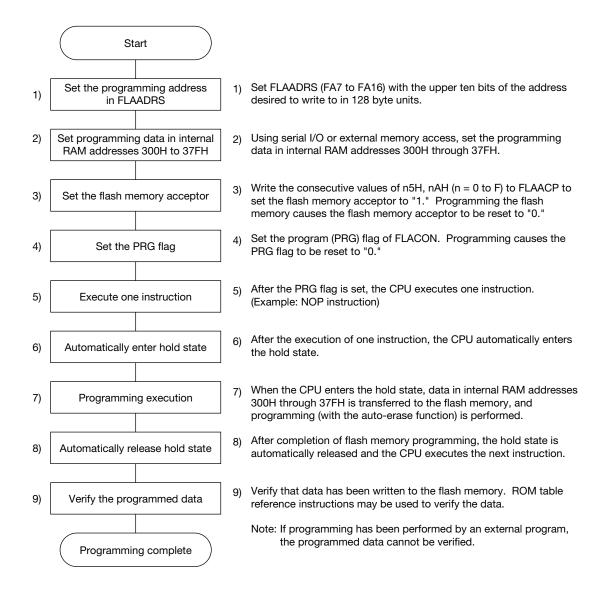

| 19.6.4  | User Mode Programming Example                            |  |

| (1)     | User mode programming flowchart example                  |  |

| (2)     | User mode programming program example                    |  |

| 19.6.5  | Notes on Use of User Mode                                |  |

| 19.7 No | otes on Program                                          |  |

| (1)     | Programming of flash memory immediately after power-on . |  |

| (2)     | Note on STOP mode release                                |  |

| (3)     | Supply voltage sense reset function                      |  |

#### Chapter 20 Electrical Characteristics

| 20.1 Absolute Maximum Ratings                                         |       |

|-----------------------------------------------------------------------|-------|

| 20.2 Recommended Operating Conditions                                 |       |

| 20.3 Allowable Output Current Values                                  |       |

| 20.4 Internal Flash ROM Programming Conditions                        |       |

| 20.5 DC Characteristics                                               |       |

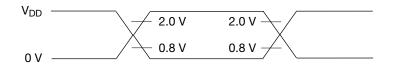

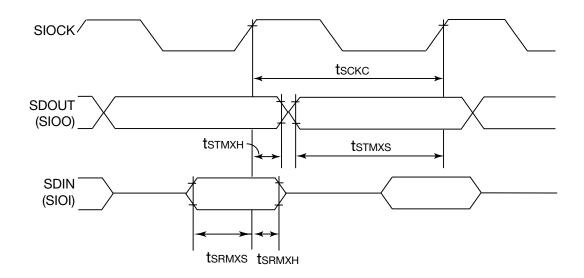

| 20.5.1 DC Characteristics ( $V_{DD}$ = 4.5 to 5.5 V)                  |       |

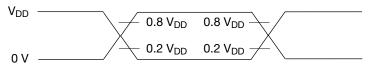

| 20.5.2 DC Characteristics ( $V_{DD}$ = 2.4 to 3.6 V)                  |       |

| 20.6 AC Characteristics                                               |       |

| 20.6.1 AC Characteristics ( $V_{DD}$ = 4.5 to 5.5 V)                  |       |

| 20.6.2 AC Characteristics ( $V_{DD}$ = 2.4 to 3.6 V)                  |       |

| 20.7 A/D Converter Characteristics                                    |       |

| 20.7.1 A/D Converter Characteristics (V <sub>DD</sub> = 4.5 to 5.5 V) | 20-23 |

| 20.7.2 A/D Converter Characteristics (V <sub>DD</sub> = 2.4 to 3.6 V) | 20-23 |

| 20.8 D/A Converter Characteristics                                    |       |

| Chapter | 21 Special Function Registers (SFRs) |

|---------|--------------------------------------|

| 21.1    | Dverview                             |

| 21.2    | List of SFRs                         |

| Chapter | 22 Package Dimensions                |

Contents-18

| Chapter 1   | Overview                          | 1        |

|-------------|-----------------------------------|----------|

| Chapter 1   | Gverview                          |          |

| Chapter 2   | CPU Architecture                  | 2        |

| Onapter 2   |                                   |          |

| Chapter 3   | CPU Control Functions             | 3        |

| Chapter 5   |                                   | Ŭ        |

| Chapter 4   | Memory Control Functions          | 4        |

| Chapter 4   | Memory Control Functions          |          |

| Chapter 5   | Port Functions                    | 5        |

| Chapter 5   | Port Functions                    | 3        |

| Chantar C   | Clask Oscillation Circuit         | 6        |

| Chapter 6   | Clock Oscillation Circuit         | 0        |

|             |                                   | 7        |

| Chapter 7   | Time Base Counter (TBC)           | 7        |

| [           |                                   |          |

| Chapter 8   | General-Purpose 8/16 Bit Timers   | 8        |

|             |                                   |          |

| Chapter 9   | Capture/Compare Timer             | 9        |

|             |                                   |          |

| Chapter 10  | Real-Time Counter (RTC)           | 10       |

|             |                                   |          |

| Chapter 11  | PWM Function                      | 11       |

| L           |                                   |          |

| Chapter 12  | Serial Port Functions             | 12       |

|             |                                   |          |

| Chapter 13  | A/D Converter Functions           | 13       |

|             |                                   |          |

| Chapter 14  | D/A Converter Functions           | 14       |

|             |                                   |          |

| Chapter 15  | Peripheral Functions              | 15       |

| Unapter 10  |                                   |          |

| Chapter 16  | External Interrupt Functions      | 16       |

| Chapter 10  |                                   |          |

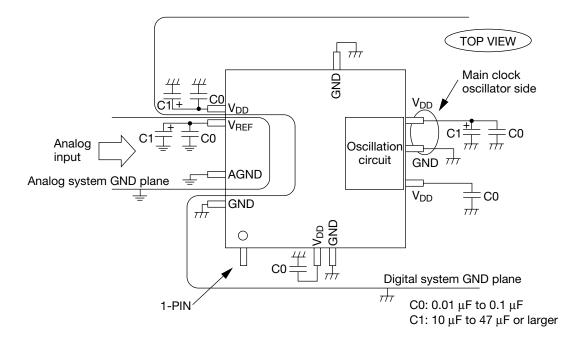

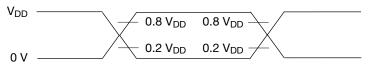

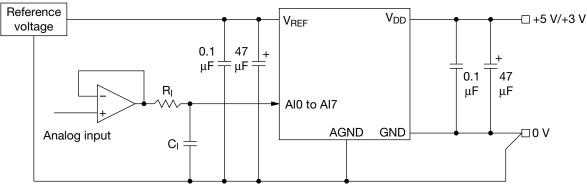

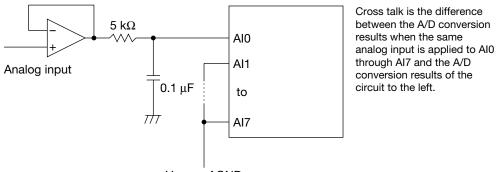

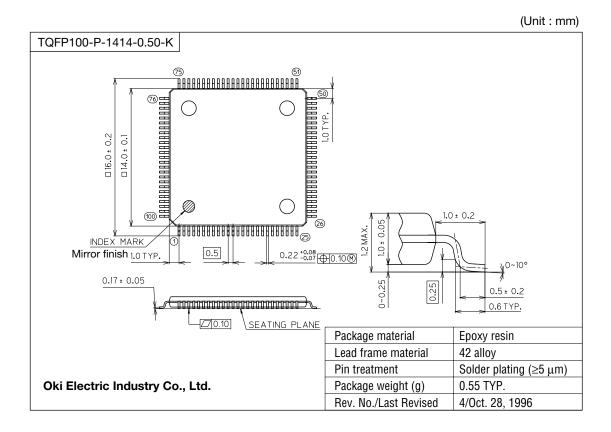

| Chapter 17  | Interrupt Dreassoing Functions    | 17       |