# PSØ8

Single-chip Solution for Weight Scales

# **Preliminary Datasheet**

July 2008 Version 0.4

# acam-messelectronic gmbh solutions in time

# **Table of Content**

| Table of Content                        | 2      | 7.2.2 RAM Write Access                    | 49  |

|-----------------------------------------|--------|-------------------------------------------|-----|

| 1 System Overview                       | 3<br>3 | 7.2.3 EEPROM Read Access / Read           |     |

| 1.1 Introduction                        | 3      | Protection                                | 50  |

| 1.2 Features                            | 3      | 7.2.4 EEPROM Write Access                 | 50  |

| 1.3 Applications                        | 3      | 8 LCD-Driver                              | 51  |

| 1.4 Architecture                        | 4      | 8.1 Basic Configuration                   | 51  |

| 2 Characteristics and Specifications    | 5      | 8.2 LCD-Power supply                      | 51  |

| 2.1 Pin Assignment                      | 5      | 8.3 LCD Output Driver configuration       | 52  |

| 2.2 Pin Description                     | 5      | 8.4 LCD Control                           | 54  |

| 2.3 Absolute Maximum Ratings            | 7      | 8.5 Connecting Schemes                    | 56  |

| 2.4 Normal Operating Conditions         | 8      | 8.6 Setting the Segment Position          | 58  |

| 2.4.1 Electrical Characterization       | 8      | 9. Converter Front-End                    | 60  |

| 2.5 Converter Precision                 | 8      | 9.1 Operating Principle                   | 60  |

| 2.5.1 Resolution vs. Supply Voltage     | 9      | 9.2 Modes and Timings                     | 61  |

| 2.5.2 Converter Precision with High Qu  |        | 9.2.1 single_conversion                   | 62  |

| Load Cell                               | 10     | 9.2.2 stretch                             | 62  |

|                                         | 12     |                                           | 63  |

| 2.6 Current Consumption                 |        | 9.2.3 cytime (Cycle Time)                 |     |

| 2.7 Timings                             | 12     | 9.2.4 avrate (Averaging Rate)             | 63  |

| 2.7.1 Oscillators                       | 12     | 9.2.5 Mode Selection Criteria             | 64  |

| 2.7.2 SPI-Interface                     | 12     | 9.3 Performance settings                  | 65  |

| 2.8 Package Information                 | 14     | 9.3.1 Resolution and AVRate               | 65  |

| 2.8.1 PAD Assignment                    | 14     | 9.3.2 Conversion Time/Measuring Rate      |     |

| 2.8.2 Bonding PAD Location (only for B  |        | (Continuous Mode)                         | 65  |

| Version)                                | 14     | 9.3.3 Conversion Time / Measuring Rate    |     |

| 2.8.3 QFN56 Package Outline             | 15     | (Single Conversion Mode)                  | 66  |

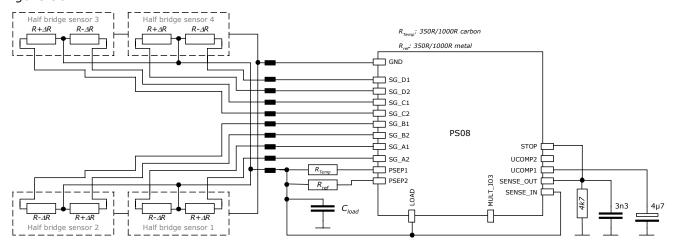

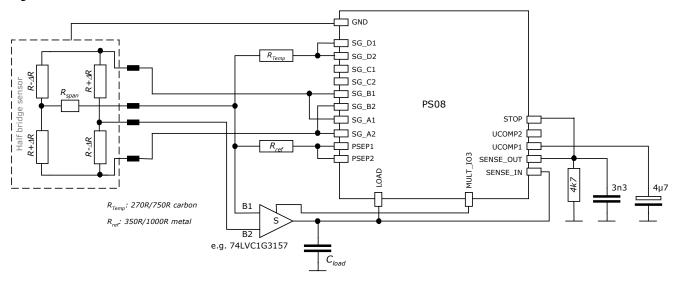

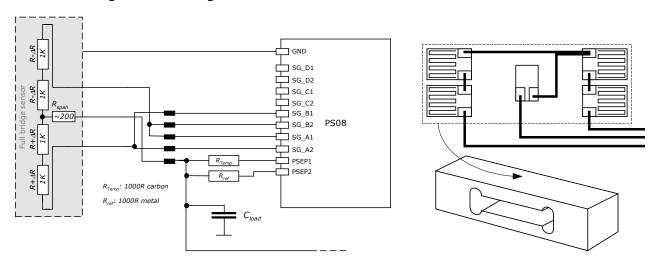

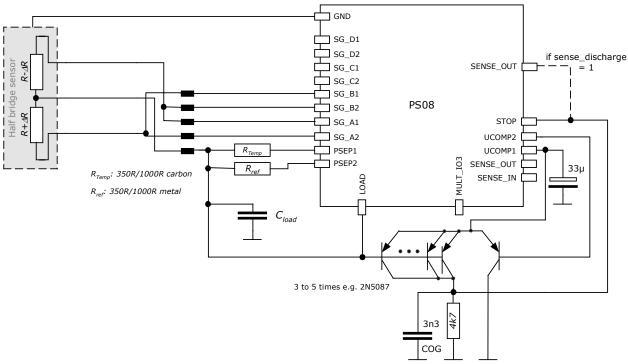

| 2.8.4 QFN56 Recommended Pad Layou       | ıt 15  | 9.4 Connecting the Strain Gage            | 66  |

| 3 Central Processing Unit (CPU)         | 16     | 9.4.1 Half Bridge Mode (connected as F    | ull |

| 3.1 Block Diagram                       | 16     | Bridge)                                   | 66  |

| 3.2 Arithmetic Logic Unit (ALU)         | 16     | 9.4.2 Full Bridge Mode                    | 67  |

| 3.2.1 Accumulators                      | 16     | 9.4.3 Quattro Bridge Mode                 | 67  |

| 3.2.2 Flags                             | 17     | 9.4.4 Wheatstone Mode                     | 68  |

| 3.3 Memory Organization                 | 17     | 9.4.5 Full Bridge as Half Bridge for Lowe | er  |

| 3.3.1 ROM and EEPROM Organization       | 17     | Current                                   | 68  |

| 3.3.2 RAM Organization                  | 18     | 9.5 Load-Capacitor (Cload)                | 69  |

| 3.3.3 RAM Address Pointer               | 18     | 9.6 The Comparator                        | 70  |

| 3.4 Register Set                        | 18     | 9.6.1 Comparator Control                  | 71  |

| 3.4.1 Configuration Registers           | 18     | 9.7 Rtemp / Rref                          | 71  |

| 3.4.2 Result Registers                  | 26     | 9.7.1 Correction of Comparator Delay      | 71  |

| 3.4.3 Status Register                   | 27     | 9.7.2 Temperature Measurement             | 72  |

| 3.5 Instruction Set                     | 28     | 9.7.3 Values for Rtemp and Rref           | 72  |

| 4 System Reset, Sleep Mode and Auto-    |        | 9.8 Post-processing                       | 72  |

| configuration                           | 45     | 9.8.1 Temperature Compensation of Gai     |     |

| 4.1 Power On Reset                      | 46     | and Offset Drift of the Loadcell          | 73  |

| 4.2 Watchdog Reset                      | 46     | 9.8.2 Off-center Correction for Quattro   |     |

| 4.3 External Reset on Pin 27            | 46     | Scales                                    | 73  |

| 4.4 Sleep Mode                          | 46     | 9.8.3 Gain-Drift of PSØ8 itself           | 73  |

| 5 CPU Clock generation                  | 46     | 9.9 Highest Resolution with PSØ8          | 74  |

| 5.1 Watchdog counter and Single convers | _      | 9.10 PSØ8 with external microprocessor    | 75  |

| counter                                 | 47     | 10 Oscillators                            | 75  |

| 6 IO-pins                               | 47     | 11 Voltage Measurement                    | 76  |

| 6.1 Configuration                       | 47     | 12 Auto-on                                | 76  |

| _                                       | 47     |                                           |     |

| 6.2 Output – write                      |        | 13 Measurement Range 1                    | 76  |

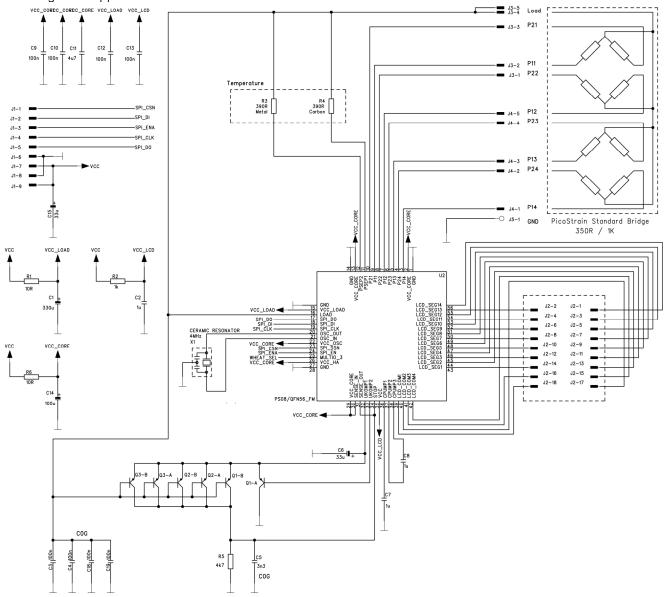

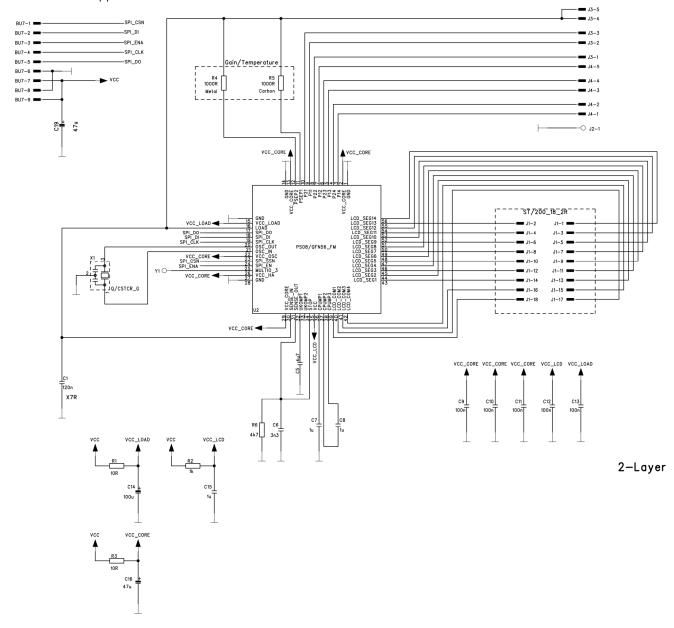

| 6.3 Input – read                        | 47     | 14 Sample Circuits                        | 77  |

| 7 SPI-Interface                         | 48     | 15 Known Bugs                             | 79  |

| 7.1 Interfacing                         | 48     | Last Changes                              | 79  |

| 7.2 SPI Timing                          | 48     | Contacts                                  | 80  |

| 7.3 SPI-Instructions                    | 49     |                                           |     |

| 7.2.1 RAM Read Access                   | 49     |                                           |     |

#### 1 System Overview

#### 1.1 Introduction

PSO8 is a System-on-Chip for ultra low-power and high resolution applications. It was designed especially for weight scales but fits also to any kind of force or torque measurements based on metal strain gages. It takes full advantage of the digital measuring principle of PICOSTRAIN. Thus it combines the performance of a 28-Bit signal converter with a 24-Bit microprocessor. Additional elements like an LCD driver, 3k ROM with many complex pre-defined functions, 1k EEPROM program memory and an integrated 10 kHz oscillator round off the device. A minimum amount of external components is necessary to build a complete weighing electronic.

With PSØ8 it is possible for the first time to build solar cell driven weight scales based on metal strain gages. A sophisticated power management and the special features of the PICOSTRAIN measuring principle can reduce the total current of the system down to 15  $\mu A$  – including the sensor current. This way the PSØ8 is perfectly suited for battery driven or solar cell driven weight scales.

On the other hand the PSØ8 offers a high resolution comparable to high-end ADC's. With maximum 1 million internal divisions (150,000 stable display divisions) it shows top performance. But it beats ADC with respect to current consumption. With PSØ8 it is possible to build legal for trade scales that run with 2 AA batteries for more than 1500 operating hours.

Throwing a glance at further specialties like software adjustment of the offset and gain compensation reveals that the PSØ8 opens the door to new and innovative product solutions.

#### 1.2 Features

- PICOSTRAIN Front-End with up to 1 Mio. eff. scale divisions (@2mV/V) = 150.000 Peak-Peak Div.

- 24-Bit Microprocessor

- 1 k x 8-Bit EEPROM program memory, read protected

- 3 k ROM powerful program code like 48 Bit multiplication and division or binary to 7segment conversion

- 8-layer hardware stack

- Embedded very low current 10 kHz oscillator

- Driver for external 4 MHz ceramic oscillator

- Standby current <1μA</li>

- 5 programmable I/O-ports

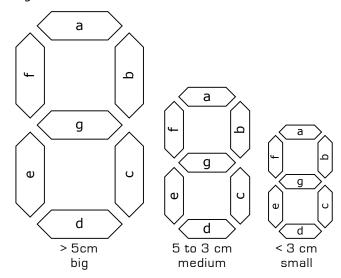

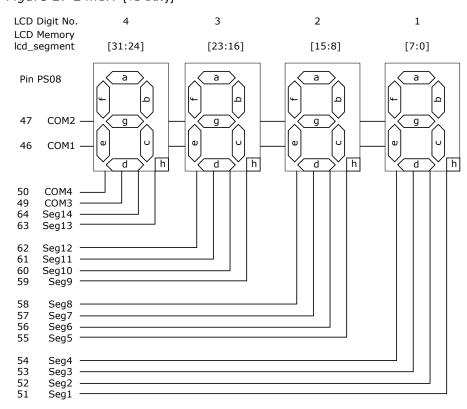

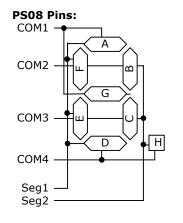

- 4 x 14, 3 x 15, 2 x 16 LCD driver

- Embedded charge pump for driving the LCD

- Embedded bandgap voltage reference for low battery detection

- Ports for temperature measurement with lowcost carbon/metal film resistors

- Watchdog timer

- Serial SPI interface

- Supply voltage 2.2 to 3.6 V at 130 dB PSRR

- System operational current down to 15  $\mu$ A

- As dice (115 µm pitch) or packaged (QFN56, 7x7 mm²)

### 1.3 Applications

#### Industrial

- Legal for trade scales

- Counting scales

- Torque indicators

- Pressure indicators

#### Consumer

- Solar scales

- Body scales

- Kitchen scales

- Postal scales

- Package scales

#### Important Note:

This datasheet is a preliminary version based on first engineering samples. It is not intended to be complete or correct in any detail. There might be major changes for the final version.

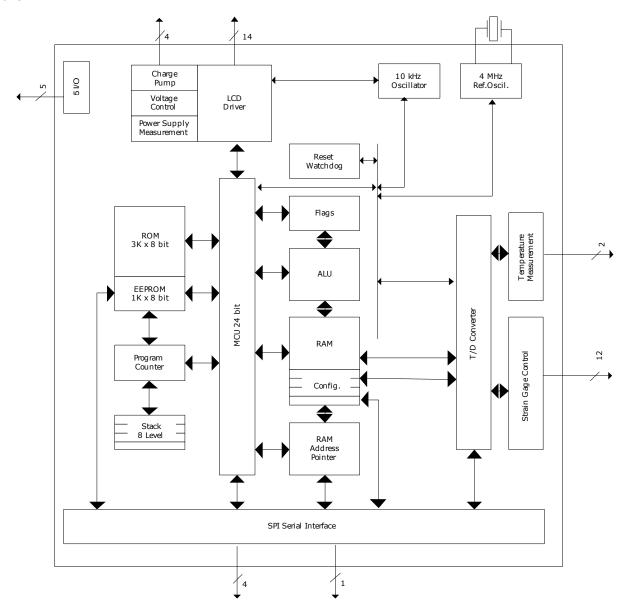

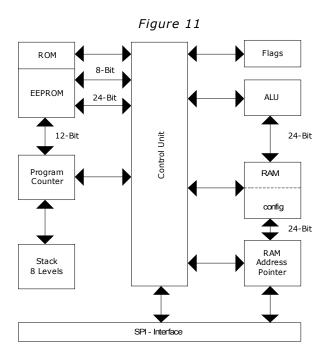

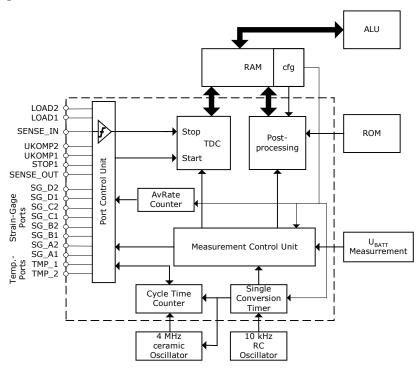

# 1.4 Architecture

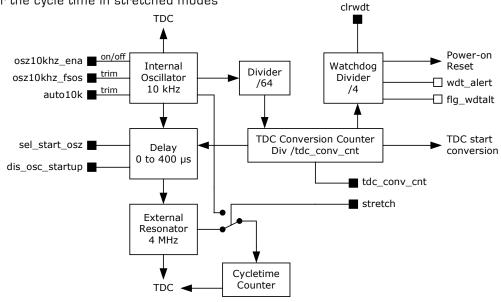

Figure 1

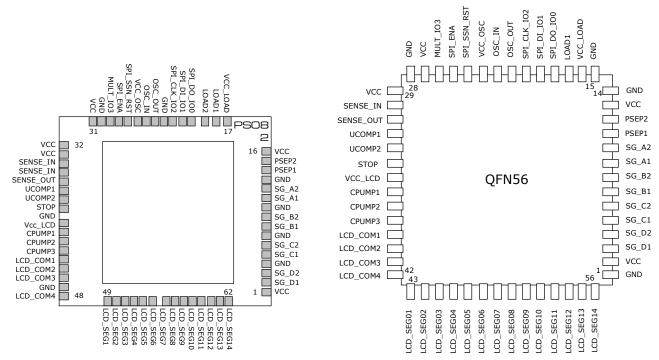

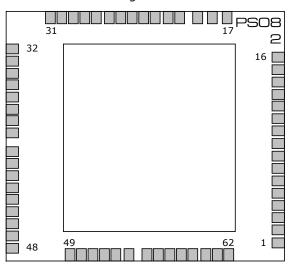

# 2 Characteristics and Specifications2.1 Pin Assignment

Figure 2

Pin Assignment

# 2.2 Pin Description

Pure dice:

| #Die | Name        | Description                                  | Туре         | If not used |

|------|-------------|----------------------------------------------|--------------|-------------|

| 1    | VCC         | Supply voltage digital part , I/O, 4MHz-osc. |              |             |

| 2    | SG_D1       | Port 1 halfbridge D                          | N Open Drain |             |

| 3    | SG_D2       | Port 2 halfbridge D                          | N Open Drain |             |

| 4    | GND         |                                              |              |             |

| 5    | SG_C1       | Port 1 halfbridge C                          | N Open Drain |             |

| 6    | SG_C2       | Port 2 halfbridge C                          | N Open Drain |             |

| 7    | GND         |                                              |              |             |

| 8    | SG_B1       | Port 1 halfbridge B                          | N Open Drain |             |

| 9    | SG_B2       | Port 2 halfbridge B                          | N Open Drain |             |

| 10   | GND         |                                              |              |             |

| 11   | SG_A1       | Port 1 halfbridge A                          | N Open Drain |             |

| 12   | SG_A2       | Port 2 halfbridge A                          | N Open Drain |             |

| 13   | GND         |                                              |              |             |

| 14   | PSEP1       | Port 1 temperature measurement               | N Open Drain |             |

| 15   | PSEP2       | Port 2 temperature measurement               | N Open Drain |             |

| 16   | VCC         | Supply voltage digital part , I/O, 4MHz-osc. |              |             |

| 17   | VCC_LOAD    | Power supply load output pins 1 and 2        |              |             |

| 18   | LOAD1       | Load output to measuring capacitor           | P Open Drain |             |

| 19   | LOAD2       |                                              | P Open Drain |             |

| 20   | SPI_SO_IOO  | Output serial SPI interface or IOO           | Mult-IO      |             |

| 21   | SPI_SI_IO1  | Input serial SPI interface or IO1            | Mult-IO      |             |

| 22   | SPI_SCK_IO2 | Clock serial SPI interface or IO2            | Mult-IO      |             |

| 23   | GND         |                                              |              |             |

| 24   | OSC_OUT     | Output to 4MHz ceramic resonator             |              |             |

| 25   | OSC_IN      | Input to 4MHz ceramic resonator              |              |             |

**PS08**

**PICO**STRAIN

Single-chip Solution for Weight Scales

| 26 | Vcc_OSC   | 4MHz Oscillator supply voltage                         | Mult-IO      |

|----|-----------|--------------------------------------------------------|--------------|

|    |           | Slave select or RST input (High active)                | Mult-IO with |

|    |           |                                                        | pull-down    |

| 28 | SPI_ENA   | Serial SPI interface enable                            | Mult-IO      |

| 29 | MULT_IO3  | Select for Wheatstone comparator Mux or IO3            |              |

|    |           | or interrupt                                           |              |

|    | GND       |                                                        |              |

|    | Vcc       |                                                        |              |

|    | Vcc       |                                                        |              |

| 33 | Vcc       | Supply voltage digital part , I/O, 4MHz-osc.           | Analog In    |

|    | SENSE_IN  | Input internal CMOS comparator                         | Analog Out   |

| 35 | SENSE_OUT | Output internal CMOS comparator                        | Analog Out   |

|    | UCOMP1    | External comparator circuit connection                 | Analog Out   |

|    | UCOMP2    | External comparator circuit connection                 | Analog In    |

|    | STOP      | Stop input measuring signal                            |              |

|    | GND       | GND                                                    |              |

| 40 | VCC_LCD   | Supply voltage LCD, 10kHz osc., bandgap                |              |

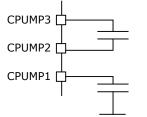

|    | CPUMP1    | LCD voltage doubling and stabilization                 | Analog Out   |

|    | CPUMP2    | LCD voltage doubling and stabilization                 | Analog Out   |

|    | CPUMP3    | LCD voltage doubling and stabilization                 | Analog Out   |

| 44 | LCD_com1  | LCD line driver for 1/2, 1/3, 1/4 duty                 | LCD Buffer   |

| 45 | LCD_com2  | LCD line driver for 1/2, 1/3, 1/4 duty                 | LCD Buffer   |

| 46 | LCD_com3  | LCD line driver for 1/3, 1/4 duty, row driver for      | LCD Buffer   |

|    |           | 1/2 duty                                               |              |

|    | GND       |                                                        |              |

| 48 | LCD_com4  | LCD line driver for $1/4$ duty, row driver for $1/2$ , | LCD Buffer   |

|    |           | 1 /3 duty                                              |              |

| 49 | LCD_seg1  | LCD row driver                                         | LCD Buffer   |

| 50 | LCD_seg2  | LCD row driver                                         | LCD Buffer   |

| 51 | LCD_seg3  | LCD row driver                                         | LCD Buffer   |

| 52 | LCD_seg4  | LCD row driver                                         | LCD Buffer   |

| 53 | LCD_seg5  | LCD row driver                                         | LCD Buffer   |

| 54 | LCD_seg6  | LCD row driver                                         | LCD Buffer   |

| 55 | LCD_seg7  | LCD row driver                                         | LCD Buffer   |

| 56 | LCD_seg8  | LCD row driver                                         | LCD Buffer   |

| 57 | LCD_seg9  | LCD row driver                                         | LCD Buffer   |

| 58 | LCD_seg10 | LCD row driver                                         | LCD Buffer   |

| 59 | LCD_seg11 | LCD row driver                                         | LCD Buffer   |

| 60 | LCD_seg12 | LCD row driver                                         | LCD Buffer   |

| 61 | LCD_seg13 | LCD row driver                                         | LCD Buffer   |

| 62 | LCD_seg14 | LCD row driver                                         | LCD Buffer   |

# Packed, QFN56:

| #QFN | Name  | Description                                  | Туре         | If not used |

|------|-------|----------------------------------------------|--------------|-------------|

| 1    | GND   | Ground                                       |              |             |

| 2    | Vcc   | Supply voltage digital part , I/O, 4MHz-osc. |              |             |

| 3    | SG_D1 | Port 1 halfbridge D                          | N Open Drain |             |

| 4    | SG_D2 | Port 2 halfbridge D                          | N Open Drain |             |

| 5    | SG_C1 | Port 1 halfbridge C                          | N Open Drain |             |

| 6    | SG_C2 | Port 2 halfbridge C                          | N Open Drain |             |

| 7    | SG_B1 | Port 1 halfbridge B                          | N Open Drain |             |

| 8    | SG_B2 | Port 2 halfbridge B                          | N Open Drain |             |

| 9    | SG_A1 | Port 1 halfbridge A                          | N Open Drain |             |

| 10   | SG_A2 | Port 2 halfbridge A                          | N Open Drain |             |

| 11   | PSEP1 | Port 1 temperature measurement               | N Open Drain |             |

| 12   | PSEP2 | Port 2 temperature measurement               | N Open Drain |             |

| 13   | Vcc   | Supply voltage digital part , I/O, 4MHz-osc. |              |             |

| 14   | GND   | Ground                                       |              |             |

| 15 | GND         | Ground                                                 |              |

|----|-------------|--------------------------------------------------------|--------------|

| 16 | Vcc_load    | Power supply load output pins 1 and 2                  |              |

| 17 | Load1       | Load output to measuring capacitor                     | P Open Drain |

| 18 | SPI_SO_IOO  | Output serial SPI interface or IOO                     | Mult-IO      |

| 19 | SPI_SI_IO1  | Input serial SPI interface or IO1                      | Mult-IO      |

| 20 | SPI_SCK_IO2 | Clock serial SPI interface or IO2                      | Mult-IO      |

| 21 | OSC_OUT     | Output to 4MHz ceramic resonator                       | ividio io    |

| 22 | OSC_IN      | Input to 4MHz ceramic resonator                        |              |

| 23 | Vcc_OSC     | 4MHz Oscillator supply voltage                         | Mult-IO      |

| 24 | SPI_CSN_RST | Slave select or RST input (High active)                | Mult-IO with |

|    |             |                                                        | pull-down    |

| 25 | SPI_ENA     | Serial SPI interface enable                            | Mult-IO      |

| 26 | MULT_IO3    | Select for Wheatstone comparator Mux or IO3            |              |

|    | _           | or interrupt                                           |              |

| 27 | Vcc         | ·                                                      |              |

| 28 | GND         | GND                                                    |              |

| 29 | Vcc         | Supply voltage digital part , I/O, 4MHz-osc.           | Analog In    |

| 30 | SENSE_IN    | Input internal CMOS comparator                         | Analog Out   |

| 31 | SENSE_OUT   | Output internal CMOS comparator                        | Analog Out   |

| 32 | UCOMP1      | External comparator circuit connection                 | Analog Out   |

| 33 | UCOMP2      | External comparator circuit connection                 | Analog In    |

| 34 | STOP        | Stop input measuring signal                            |              |

|    | GND         | GND                                                    |              |

| 35 | VCC_LCD     | Supply voltage LCD, 10kHz osc., bandgap                |              |

| 36 | CPUMP1      | LCD voltage doubling and stabilization                 | Analog Out   |

| 37 | CPUMP2      | LCD voltage doubling and stabilization                 | Analog Out   |

| 38 | CPUMP3      | LCD voltage doubling and stabilization                 | Analog Out   |

| 39 | LCD_com1    | LCD line driver for 1/2, 1/3, 1/4 duty                 | LCD Buffer   |

| 40 | LCD_com2    | LCD line driver for 1/2, 1/3, 1/4 duty                 | LCD Buffer   |

| 41 | LCD_com3    | LCD line driver for 1/3, 1/4 duty, row driver for      | LCD Buffer   |

|    |             | 1/2 duty                                               |              |

| 42 | LCD_com4    | LCD line driver for $1/4$ duty, row driver for $1/2$ , | LCD Buffer   |

|    |             | 1 /3 duty                                              |              |

| 43 | LCD_seg1    | LCD row driver                                         | LCD Buffer   |

| 44 | LCD_seg2    | LCD row driver                                         | LCD Buffer   |

| 45 | LCD_seg3    | LCD row driver                                         | LCD Buffer   |

| 46 | LCD_seg4    | LCD row driver                                         | LCD Buffer   |

| 47 | LCD_seg5    | LCD row driver                                         | LCD Buffer   |

| 48 | LCD_seg6    | LCD row driver                                         | LCD Buffer   |

| 49 | LCD_seg7    | LCD row driver                                         | LCD Buffer   |

| 50 | LCD_seg8    | LCD row driver                                         | LCD Buffer   |

| 51 | LCD_seg9    | LCD row driver                                         | LCD Buffer   |

| 52 | LCD_seg10   | LCD row driver                                         | LCD Buffer   |

| 53 | LCD_seg11   | LCD row driver                                         | LCD Buffer   |

| 54 | LCD_seg12   | LCD row driver                                         | LCD Buffer   |

| 55 | LCD_seg13   | LCD row driver                                         | LCD Buffer   |

| 56 | LCD_seg14   | LCD row driver                                         | LCD Buffer   |

# 2.3 Absolute Maximum Ratings

| Symbol   | Parameter           | Conditions      | Min  | Max       | Unit |

|----------|---------------------|-----------------|------|-----------|------|

| Vcc      | Supply voltage      | Vcc vs. GND     | -0.5 | 5.0       | V    |

| Vcc_load |                     |                 |      |           |      |

| Vcc_osc  |                     |                 |      |           |      |

| Vcc_LCD  |                     |                 |      |           |      |

| Vin      | DC input voltage    |                 | -0.5 | Vcc + 0.5 | V    |

| Tstg     | Storage Temperature | Plastic package | -55  | 150       | Ô    |

# 2.4 Normal Operating Conditions

| Symbol   | Parameter             | Conditions                    | Min    | Max | Unit |

|----------|-----------------------|-------------------------------|--------|-----|------|

| Vcc      | Supply voltage        | Vcc vs. GND                   | 2.2    | 3.6 | V    |

| Vcc_load |                       |                               | (1.5*) |     |      |

| Vcc_osc  |                       | (* without EEPROM programming | , ,    |     |      |

| Vcc_LCD  |                       | and voltage measurement)      |        |     |      |

| Vin      | DC input voltage      |                               | 0.0    | Vcc | V    |

| Vout     | Output voltage        |                               | 0.0    | Vdd | V    |

| Тор      | Operating temperature |                               | -40    | 125 | °C   |

| Tstg     | Storage temperature   | Plastic package               | -55    | 150 | °C   |

#### 2.4.1 Electrical Characterization

| Symbol  | Parameter                     | Conditions  | Min    | Тур. | Max    | Unit |

|---------|-------------------------------|-------------|--------|------|--------|------|

| Vil     | Input low voltage             | CMOS        |        |      | 0.3Vcc | V    |

| Vih     | Input high voltage            | CMOS        | 0.7Vcc |      |        |      |

| Vhyst   | Input hysteresys              | Vcc = 3.6 V |        | 400  |        | mV   |

|         |                               | Vcc = 3.0 V |        | 280  |        |      |

|         |                               | Vcc = 2.7 V |        | 225  |        |      |

|         |                               | Vcc = 2.2 V |        | 150  |        |      |

|         |                               | Vcc = 1.8 V |        | 80   |        |      |

| Voh     | Output high voltage           |             | 8.0    |      |        | V    |

| Vol     | Output low voltage            |             |        |      | 0.2Vcc | V    |

| VIbat   | Low battery voltage detect    |             | 2.2    |      | 2.9    | V    |

| LCD_com | LCD driver Voltage stabilized | lcd_vlt = 0 |        | 2.0  |        | V    |

| LCD_seg |                               | lcd_vlt = 1 |        | 2.5  |        |      |

|         |                               | lcd_vlt = 2 |        | 3.0  |        |      |

#### 2.5 Converter Precision

The following tables show the measurement capability for the PS $\emptyset 8$ .

Table 1 Performance at Vcc = 3.6 V with external comparator

|           | ENOB <b>dR/F</b> | R strain re | sistance | Resolution ( | □ 2 mV/V m | ax. out, <b>Fas</b> | t settle  |

|-----------|------------------|-------------|----------|--------------|------------|---------------------|-----------|

| Frequency | No filter        | SINC3       | SINC5    | ENOB         | Divisions  | Noise nV            | Noise nV  |

| (Hz)      |                  |             |          |              | effective  | rms                 | peak-peak |

| 500       | 23.8             | 24.8        | 25.2     | 14.8         | 28,000     | 231                 | 1,386     |

| 250       | 24.4             | 25.2        | 25.7     | 15.4         | 44,000     | 148                 | 891       |

| 100       | 25.2             | 25.8        | 26.1     | 16.2         | 74,000     | 89                  | 535       |

| 50        | 25.5             | 26.2        | 26.5     | 16.5         | 95,000     | 69                  | 416       |

| 20        | 26.0             | 26.8        | 27.0     | 17.0         | 133,000    | 49                  | 297       |

| 10        | 26.6             | 27.4        | 27.7     | 17.6         | 200,000    | 33                  | 198       |

| 5         | 27.2             | 27.9        | 28.3     | 18.2         | 294,000    | 22                  | 135       |

|           | Resolution ( | @ 2 mV/V m | ax. out, <i>SIN</i> | IC3 Filter | Resolution ( | □ 2 mV/V m | ax. out, <i>SIN</i> | IC5 Filter |

|-----------|--------------|------------|---------------------|------------|--------------|------------|---------------------|------------|

| Frequency | ENOB         | Divisions  | Noise nV            | Noise nV   | ENOB         | Divisions  | Noise nV            | Noise nV   |

| (Hz)      |              | effective  | rms                 | peak-peak  |              | effective  | rms                 | peak-peak  |

| 500       | 15.8         | 55,000     | 118                 | 713        | 16.2         | 74,000     | 89                  | 535        |

| 250       | 16.2         | 74,000     | 89                  | 535        | 16.7         | 105,000    | 62                  | 376        |

| 100       | 16.8         | 114,000    | 57                  | 347        | 17.1         | 142,000    | 46                  | 277        |

| 50        | 17.2         | 153,000    | 42                  | 257        | 17.5         | 181,000    | 36                  | 218        |

| 20        | 17.8         | 222,000    | 29                  | 178        | 18.0         | 266,000    | 24                  | 149        |

| 10        | 18.4         | 344,000    | 19                  | 115        | 18.7         | 416,000    | 15                  | 95         |

| 5         | 18.9         | 476,000    | 13                  | 83         | 19.3         | 625,000    | 10                  | 63         |

Table 2 Performance at Vcc = 3.6 V with internal comparator

|           | ENOB <b>dR/R strain resistance</b> |       |       |  | Resolution @ | <sup>3</sup> 2 mV/V m | ax. out, <b>Fas</b> | t settle  |

|-----------|------------------------------------|-------|-------|--|--------------|-----------------------|---------------------|-----------|

| Frequency | No filter                          | SINC3 | SINC5 |  | ENOB         | Divisions             | Noise nV            | Noise nV  |

| (Hz)      |                                    |       |       |  |              | effective             | rms                 | peak-peak |

| 500       | 23.0                               | 24.0  | 24.4  |  | 14.0         |                       |                     |           |

| 250       | 23.6                               | 24.4  | 25.1  |  | 14.6         |                       |                     |           |

| 100       | 24.4                               | 25.0  | 25.3  |  | 15.4         |                       |                     |           |

| 50        | 24.7                               | 25.4  | 25.7  |  | 15.7         |                       |                     |           |

| 20        | 25.2                               | 26.0  | 26.2  |  | 16.2         |                       |                     |           |

| 10        | 25.8                               | 26.6  | 26.9  |  | 16.8         |                       |                     |           |

| 5         | 26.4                               | 27.1  | 27.5  |  | 17.4         |                       |                     |           |

Table 3 General

| Symbol | Parameter                               | Conditions                                                                                      | Min          | Тур             | Max    | Unit                  |

|--------|-----------------------------------------|-------------------------------------------------------------------------------------------------|--------------|-----------------|--------|-----------------------|

| INL    | Integral Non-linearity                  |                                                                                                 |              |                 | 0.0015 | % of FS               |

|        | Offset drift  Gain drift  over 0°C 70°C | Total system, 1 k $\Omega$ DMS, 3V Full-bridge Half-bridge * Total System. 1 K $\Omega$ DMS, 5V |              | 15<br>15<br>< 1 |        | nV/K<br>nV/K<br>ppm/K |

| PSSR   | Power Supply Rejection<br>Ratio Vcc     | 1.8V or 3.3 V +-0.3 V                                                                           | 106<br>@1.8V | 130<br>@3.3V    |        | dB                    |

<sup>\*</sup> if using recommended circuit

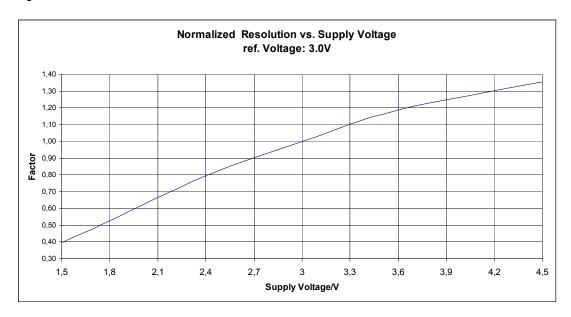

# 2.5.1 Resolution vs. Supply Voltage

PSØ8 can be driven over a very large supply voltage range. The resolution depends on the supply voltage. The higher the supply voltage the higher the achievable resolution. The diagram below shows the resolution vs. supply voltage which can be achieved with PSØ8. The values refer to 3.0 V.

Figure 3

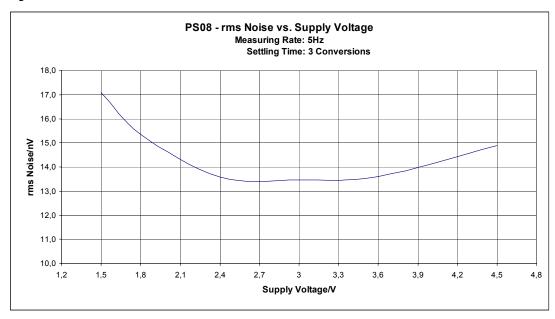

Following diagram shows how the input equivalent noise depends on the supply voltage. The lowest input noise is archived between 2.4 V and 3.6 V. The maximum differential input voltage (e.g. 6.6 mV @ 2mV/V and 3.3 V supply voltage) divided by the input noise gives the effective resolution.

Figure 4

# 2.5.2 Converter Precision with High Quality Load Cell

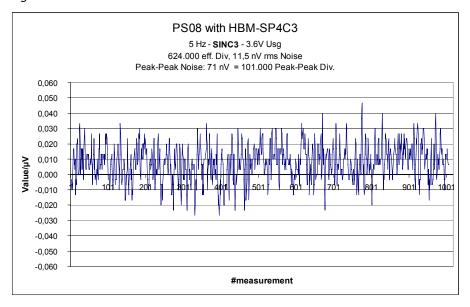

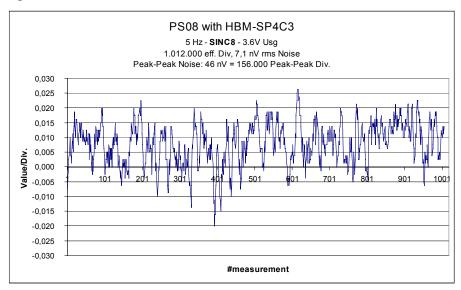

The following diagrams show measurement data of PSØ8 in combination with a C3 legal-for-trade load cell. With a SINC8 filter up to 1.000.000 internal scale divisions can be achieved. This is sufficient to realize more than 150.000 stable scale divisions. Please note that these values are captured with a high quality load cell.

|                     | Fast settle | SINC3   | SINC5   | SINC8     |

|---------------------|-------------|---------|---------|-----------|

| effective Divisions | 357.000     | 624.000 | 811.000 | 1.012.000 |

| RMS-Noise/nV        | 20,1        | 11,5    | 8,9     | 7,1       |

| effective Bits      | 18,4        | 19,3    | 19,6    | 19,9      |

Figure 5

Figure 6

**PICO**STRAIN

Single-chip Solution for Weight Scales

# 2.6 Current Consumption

The following table shows the total current consumption of the scale including all currents.

| Divisions * * | Update | Double | Operating C | urrent @ 3V | Scale type                | Operating hours |

|---------------|--------|--------|-------------|-------------|---------------------------|-----------------|

|               | Rate   | Tara*  |             |             |                           |                 |

| 2,000         | 3 Hz   | yes    | 1 kOhm      | 15 μΑ       | Solar                     |                 |

| 2,000         | 5 Hz   | yes    | 1 kOhm      | 60 µA       | Postal, Body,             | 3,000 hours     |

|               |        |        | 350 Ohm     | 90 µA       | Kitchen , Pocket          | (1xCR2032)      |

| 5,000         | 5 Hz   | yes    | 1 kOhm      | 120 µA      | High-end postal, Kitchen, | 1,500 hours     |

|               |        |        | 350 Ohm     | 220 µA      | Pocket                    | (1xCR2032)      |

| 10,000        | 5 Hz   | yes    | 1 kOhm      | 300 µA      | High-end pocket,          | 2,000 hours     |

|               |        |        | 350 Ohm     | 700 µA      | Counting                  | (1xCR2430)      |

| 80,000        | 5 Hz   | no     | 1 kOhm      | 1.9 mA      | Counting                  | 1,500hours      |

|               |        |        | 350 Ohm     | 4.5 mA      | _                         | 2 x AA          |

<sup>\*</sup> With double Tara there is no overload of the load cell if tara is set at max. load and additional max. load is put on the scale. In other words the sensor output is 1 mV/V only at maximum load (no = 2 mV/V @ max load).

# 2.7 Timings

At Vcc = 3,3,  $V \pm 0.3V$ , Ta  $-40^{\circ}$ C to  $+85^{\circ}$ C unless otherwise specified

#### 2.7.1 Oscillators

Table 3 Oscillator timing

| . 45.0 0 00 | , emaser sminig                                 |     |     |     |       |

|-------------|-------------------------------------------------|-----|-----|-----|-------|

| Symbol      | Parameter                                       | Min | Тур | Max | Units |

| Clk10kHz    | 10 kHz reference oscillator                     |     | 10  |     | kHz   |

| to10st      | Oscillator start-up                             |     |     |     | μs    |

| CIkHS       | High-speed reference oscillator                 |     | 4   |     | MHz   |

| toHSst      | Oscillator start-up time with ceramic resonator |     | 50  | 150 | us    |

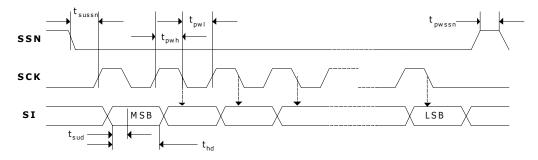

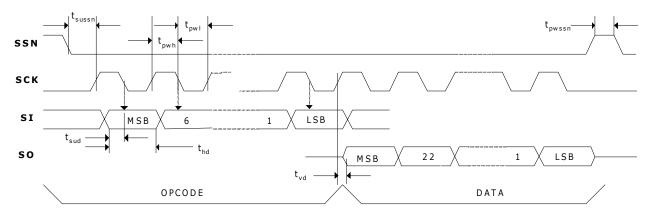

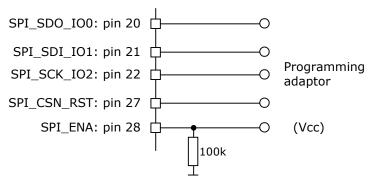

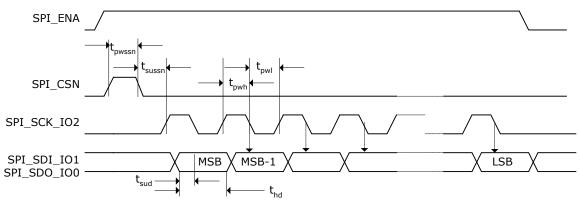

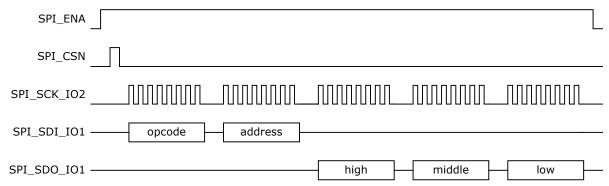

#### 2.7.2 SPI-Interface

Table 4 Serial interface timing

| I dbic + oc | i di ilitei lace tilling               |     |     |     |       |

|-------------|----------------------------------------|-----|-----|-----|-------|

| Symbol      | Parameter                              | Min | Тур | Max | Units |

| fclk        | Serial clock frequency                 |     |     | 1   | MHz   |

| tpwh        | Serial clock, pulse width high         | 500 |     |     | ns    |

| tpwl        | Serial clock, pulse width low          | 500 |     |     | ns    |

| tsussn      | SSN enable to valid latch clock        | 500 |     |     | ns    |

| tpwssn      | SSN pulse width between write cycles   | 500 |     |     | ns    |

| thssn       | SSN hold time after SCLK falling       |     |     |     |       |

| tsud        | Data set-up time prior to SCLK falling | 30  |     |     | ns    |

| thd         | Data hold time before SCLK falling     | 30  |     |     | ns    |

| tvd         | Data valid after SCLK rising           |     |     |     | ns    |

|             |                                        |     |     |     |       |

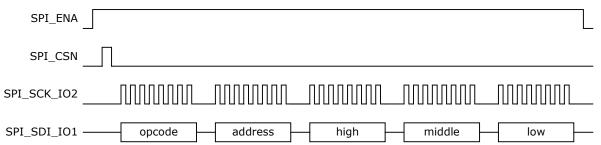

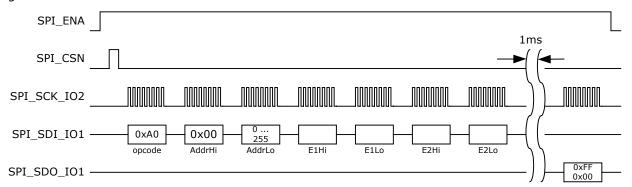

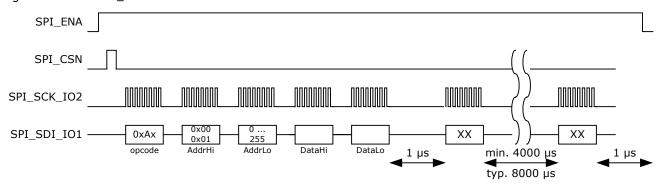

Serial Interface (SPI compatible, Clock Phase Bit =1, Clock Polarity Bit =0):

<sup>\* \*</sup> Divisions are peak-peak values with 5 Sigma (e. g. 80.000 divisions are 400.000 bits of effective resolution)

Figure 7 Write

Figure 8 Read

# 2.8 Package Information

# 2.8.1 PAD Assignment

Figure 9

# 2.8.2 Bonding PAD Location (only for Beta Version)

| Tab      | le 6 Pad location |        |        |          |      |           |        |        |          |

|----------|-------------------|--------|--------|----------|------|-----------|--------|--------|----------|

| Pac<br># | l Name            | X [µm] | Y [µm] | Position | Pad# | Name      | X      | Y      | Position |

| 1        | VCC               | 2583.8 | 193.8  | right    | 32   | VCC       | 83     | 2003.3 | left     |

| 2        | SG_D1             | 2583.8 | 316    | right    | 33   | VCC       | 83     | 1891.3 | left     |

| 3        | SG_D2             | 2583.8 | 431    | right    | 34   | SENSE_IN  | 83     | 1779.3 | left     |

| 4        | GND               | 2583.8 | 546    | right    | 35   | SENSE_OUT | 83     | 1667.3 | left     |

| 5        | SG_C1             | 2583.8 | 661    | right    | 36   | UCOMP1    | 83     | 1555.3 | left     |

| 6        | SG_C2             | 2583.8 | 776    | right    | 37   | UCOMP2    | 83     | 1443.3 | left     |

| 7        | GND               | 2583.8 | 891    | right    | 38   | STOP      | 83     | 1331.3 | left     |

| 8        | SG_B1             | 2583.8 | 1006   | right    | 39   | GND       | 83     | 1219.3 | left     |

| 9        | SG_B2             | 2583.8 | 1121   | right    | 40   | VCC_LCD   | 83     | 1045   | left     |

| 10       | GND               | 2583.8 | 1236   | right    | 41   | CPUMP1    | 83     | 933    | left     |

| 11       | SG_A1             | 2583.8 | 1351   | right    | 42   | CPUMP2    | 83     | 821    | left     |

| 12       | SG_A2             | 2583.8 | 1466   | right    | 43   | CPUMP3    | 83     | 709    | left     |

| 13       | GND               | 2583.8 | 1581   | right    | 44   | LCD_com1  | 83     | 597    | left     |

| 14       | PSEP1             | 2583.8 | 1696   | right    | 45   | LCD_com2  | 83     | 485    | left     |

| 15       | PSEP2             | 2583.8 | 1811   | right    | 46   | LCD_com3  | 83     | 373    | left     |

| 16       | VCC               | 2583.8 | 1926   | right    | 47   | GND       | 83     | 261    | left     |

| 17       | VCC_LOAD          | 2115   | 2286   | up       | 48   | LCD_com4  | 83     | 149    | down     |

| 18       | LOAD1             | 1976.6 | 2286   | up       | 49   | LCD_SEG1  | 612.6  | 83     | down     |

| 19       | LOAD2             | 1835   | 2286   | up       | 50   | LCD_SEG2  | 724.6  | 83     | down     |

| 20       | SPI_SO_IOO        | 1656.2 | 2286   | up       | 51   | LCD_SEG3  | 836.6  | 83     | down     |

| 21       | SPI_SI_IO1        | 1544.2 | 2286   | up       | 52   | LCD_SEG4  | 948.6  | 83     | down     |

| 22       | SPI_SCK_IO2       | 1432.2 | 2286   | up       | 53   | LCD_SEG5  | 1060.6 | 83     | down     |

| 23       | GND               | 1320.2 | 2286   | up       | 54   | LCD_SEG6  | 1172.6 | 83     | down     |

| 24       | OSC_OUT           | 1208.2 | 2286   | up       | 55   | LCD_SEG7  | 1347   | 83     | down     |

| 25       | OSC_IN            | 1096.2 | 2286   | up       | 56   | LCD_SEG8  | 1459   | 83     | down     |

| 26       | VCC_OSC           | 984.2  | 2286   | up       | 57   | LCD_SEG9  | 1571   | 83     | down     |

| 27       | SPI_CSN_RST       | 872.2  | 2286   | up       | 58   | LCD_SEG10 | 1683   | 83     | down     |

| 28       | SPI_ENA           | 760.2  | 2286   | up       | 59   | LCD_SEG11 | 1795   | 83     | down     |

| 29       | MULT_IO3          | 648.2  | 2286   | up       | 60   | LCD_SEG12 | 1907   | 83     | down     |

| 30       | GND               | 536.2  | 2286   | up       | 61   | LCD_SEG13 | 2019   | 83     | down     |

| 31       | VCC               | 424.2  | 2286   | up       | 62   | LCD_SEG14 | 2131   | 83     | down     |

PAD#: 56; Pad opening:  $90\mu m$  width,  $116\mu m$  height; Die size:  $2770 \times 2520 \mu m^2$

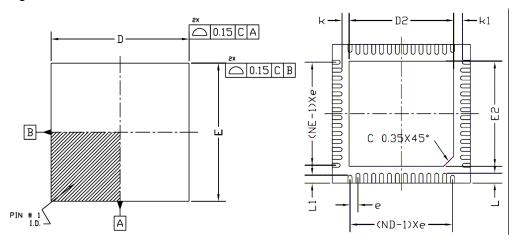

# 2.8.3 QFN56 Package Outline

QFN56, 7x7 mm<sup>2</sup>, 0.4mm Pitch

Figure 10

| S      | COMMON  |            |      |                 |          |       |  |  |  |  |  |

|--------|---------|------------|------|-----------------|----------|-------|--|--|--|--|--|

| ¥ 80 L | DIMENSI | ONS MILLIM | ETER | DIMENSIONS INCH |          |       |  |  |  |  |  |

| ü      | MIN.    | N□M.       | MAX. | MIN.            | N□M.     | MAX.  |  |  |  |  |  |

| Α      | 0.70    | 0.75       | 0.80 | 0.027           | 0.029    | 0.031 |  |  |  |  |  |

| A2     |         | 0.200 RE   | F.   | 0               | .0078 RE | F.    |  |  |  |  |  |

| b      | 0.15    | 0.20       | 0.25 | 0.006           | 0.008    | 0.010 |  |  |  |  |  |

| D      | 6.90    | 7.00       | 7.10 | 0.271           | 0.275    | 0.279 |  |  |  |  |  |

| DS     | 5.20    | 5.30       | 5.40 | 0.205           | 0.209    | 0.213 |  |  |  |  |  |

| е      |         | 0.40 TYP   |      | (               | 0.016 TY | >     |  |  |  |  |  |

| Ε      | 6.90    | 7.00       | 7.10 | 0.271           | 0.275    | 0.279 |  |  |  |  |  |

| E5     | 5.20    | 5.30       | 5.40 | 0.205           | 0.209    | 0.213 |  |  |  |  |  |

| k      | 0.25    | 0.35       | 0.45 | 0.010           | 0.014    | 0.018 |  |  |  |  |  |

| k1     | 0.35    | 0.45       | 0.55 | 0.014           | 0.018    | 0.022 |  |  |  |  |  |

| L      | 0.40    | 0.50       | 0.60 | 0.016           | 0.020    | 0.024 |  |  |  |  |  |

| L1     | 0.30    | 0.40       | 0.50 | 0.012           | 0.016    | 0.020 |  |  |  |  |  |

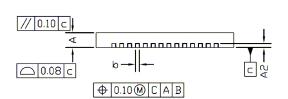

# 2.8.4 QFN56 Recommended Pad Layout

# 3 Central Processing Unit (CPU)

# 3.1 Block Diagram

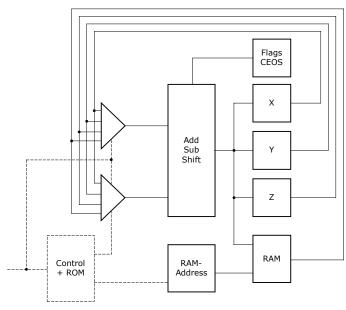

#### 3.2 Arithmetic Logic Unit (ALU)

Figure 12

#### 3.2.1 Accumulators

The ALU has three 24-Bit accumulators, X, Y and Z. The RAM is addressed by the RAM address pointer and the addressed RAM cell is used as forth accumulator. A single RAM address is mapped into the ALU by the ram address pointer. So in total there are 4 accumulators. All transfer operations (move, swap) and arithmetic-operations (shift, add, mult24...) can be applied to all accumulators.

#### 3.2.2 Flags

The processor controls 4 flags with each operation. Not-Equal and Sign flags are set with each write access to one of the accumulators (incl. RAM). Additionally, the Carry and Overflow flags are set in case of a calculation (Add/Sub/shiftR). It is possible to query each flag by a jump instruction.

- Carry

Shows the carry over in an addition or substraction. With shift operations (shiftL, rotR etc.) it shows the postponed bit.

- Not-equal zero

This flag is set to zero in case a new result unequal zero is written into an accumulator [add,sub,move,swap etc.].

- Sign

The Sign is set when a new result is written into an accumulator (add,sub,move,swap etc.) and the highest bit (MSB) is 1.

- Overflow

Indicates an overflow during an addition or substraction of two numbers in the meaning of two's complement.

#### 3.3 Memory Organization

## 3.3.1 ROM and EEPROM Organization

Table 1

| 4095 | Program Memory           |

|------|--------------------------|

|      | ROM                      |

| 1024 |                          |

| 1023 | Program Memory           |

|      | EEPROM bank 1            |

|      | EEPROM bank 2            |

|      |                          |

| 48   | Program entry            |

| 4745 | Config Reg 15 (mirrored) |

| 4442 | Config Reg 14 (mirrored) |

| 4139 | Config Reg 16 (mirrored) |

| 3835 | Config Reg 12 (mirrored) |

|      |                          |

| 53   | Config Reg 1 (mirrored)  |

| 20   | Config Reg O (mirrored)  |

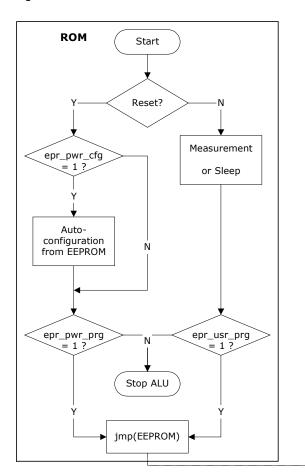

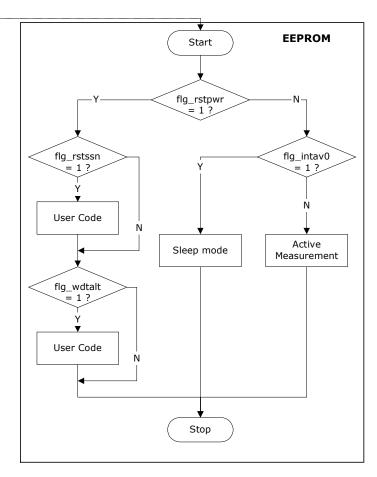

The ROM area is starting at address 1024. All computation routines needed for the PICOSTRAIN measuring method reside here. There are also further helpful routines that are frequently needed in weight scale applications, e.g. decimal to 7-segment code conversion. These routines can be called by a program in the EEPROM. The program can also jump back from the ROM to the EEPROM when configured. The EEPROM is 1024 bytes big, split in two blocks of 512 bytes. The program memory occupies 976 bytes starting from address 48. Each jump from the ROM into the EEPROM starts at address 48. The program in the EEPROM may find out the reason for the jump by means of the status information in register 22.

The lower 48 bytes in the EEPROM are reserved for an automatic configuration of the PSØ8 during a power-on reset. 3 successive bytes are added to a 24 bit word. So there are 16 words of 24 bit that can be read by the program code.

The lower bytes from 0 to 38 make 13 words of 24 bit and are used for configuration. During a power- on reset they are copied into RAM address 48 to 60.

EEPROM cells 39 to 47 are not necessary for the standard configuration. The processor can write to and read from those cells during operation (puter and getepr). They can be used for saving calibration data.

#### 3.3.2 RAM Organization

#### Table 2

| 64                                                           | Config Reg 16                                                                                                                                |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 48                                                           | <br>Config Reg O                                                                                                                             |

| 47                                                           | User RAM 47                                                                                                                                  |

| <br> 32                                                      | <br>User RAM 32                                                                                                                              |

| 31                                                           | System RAM                                                                                                                                   |

| <br>26<br>25<br>24<br>23<br>22<br>21<br>20<br>19<br>18<br>17 | System RAM UBATT CAL HB1+ Flags [p1-p2]/p2 HB0 = (A-B)+[] / (A+B)+[] HB4 = [G-H]/[G+H] HB3 = [E-F]/[E+F] HB2 = (C-D]/[C+D] HB1 = (A-B)/[A+B] |

| 15                                                           | User RAM 15                                                                                                                                  |

| <br>O                                                        | <br>User RAM O                                                                                                                               |

A..F = Discharging times at the different ports, see 3.4.2 Result Registers for more details

#### 3.3.3 RAM Address Pointer

The RAM has its own address bus with 64 addresses. The with of 24 Bit corresponds to the register width of the ALU. By means of the ram address pointer a single ram address is mapped into the ALU. It then acts as a fourth accumulator register. Changing the ram address pointer does not effect the content of the addressed ram. The RAM address pointer is modified by separate opcodes (ramadr, incramadr,...)

# 3.4 Register Set

# 3.4.1 Configuration Registers

PSØ8 has 16 configuration registers of 24 Bit width, to be addressed in the RAM from address 48 to 64. The configuration registers control the whole chip including the strain measurement and the LCD controller.

It is possible to write into the configuration registers

- By the microprocessor during operation

- Through the SPI interface from an external processor

- During the Power-on reset transferring a basic configuration from the EEPROM

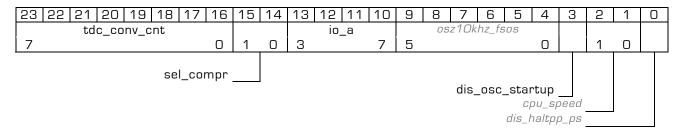

Configreg\_OO: RAM address 48 EEPROM bytes 0 - 2

acam-messelectronic gmbh©

DB\_PS08\_e\_070405

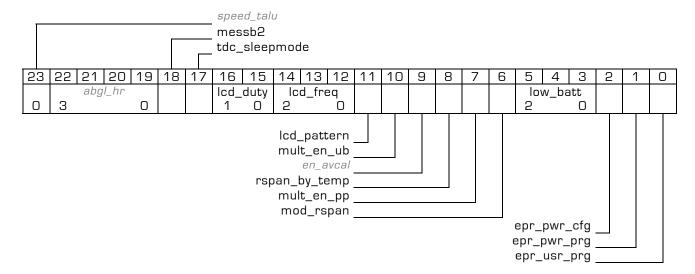

Configreg\_O1: RAM address 49 EEPROM bytes 3 - 5

Configreg\_02: RAM address 50 EEPROM bytes 6 - 8

Configreg\_O3: RAM address 51 EEPROM bytes 9 - 11

PS08

**PICO**STRAIN

Single-chip Solution for Weight Scales

Configreg 04: RAM address 52 EEPROM bytes 12 - 14

Configreg\_05: RAM address 53 EEPROM bytes 15 - 17

23 22 21 20 17 16 12 | 11 | 10 Mult\_Hb2

Configreg\_O6: RAM address 54 EEPROM bytes 18 - 20

Configreg\_07: RAM address 55 EEPROM bytes 21 - 23

23 22 21 20 13 12 11 10 Mult\_Hb4

Configreg\_08: RAM address 56 EEPROM bytes 24 - 26

Configreg\_09: RAM address 57 EEPROM bytes 27 - 29

23 22 21 20 12 | 11 | 10 Mult\_TkO

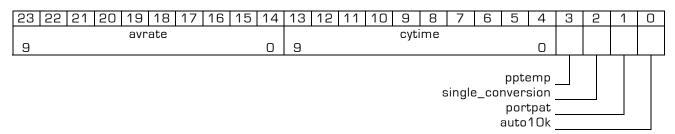

Configreg\_10: RAM address 58 EEPROM bytes 30 - 32

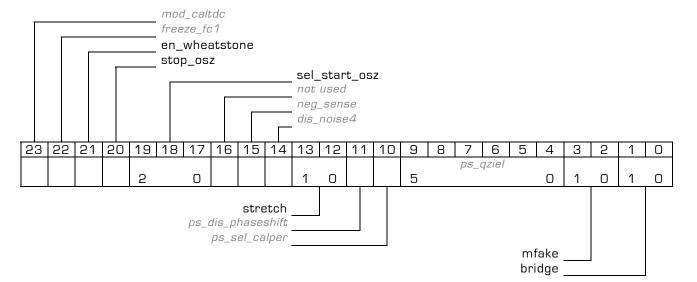

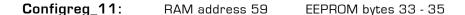

Configreg\_12: RAM address 60 EEPROM bytes 36 - 38

Configreg\_13: RAM address 61 Not mirrored in the EEPROM!

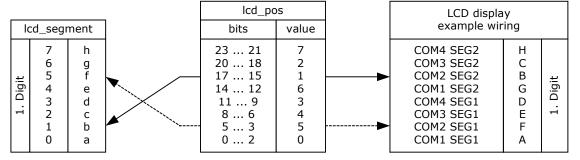

| 23 | 22          | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|-------------|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    | lcd_segment |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| 23 |             |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | 0 |

Configreg\_14: RAM address 62 EEPROM bytes 42 - 44

Configreg 15: RAM address 63 EEPROM bytes 45 - 47

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5  | 4    | 3   | 2  | 1 | 0  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|----|---|----|------|-----|----|---|----|

|    |    |    |    |    |    |    |    | bх |    |    |    |    |    |   |   |    |   | lc | d_se | gme | nt |   |    |

| 15 |    |    |    |    |    |    |    |    |    |    |    |    |    |   | 0 | 55 |   |    |      |     |    |   | 48 |

**PS08**

PICOSTRAIN

Single-chip Solution for Weight Scales

Configreg\_16: RAM address 64 EEPROM bytes 39 - 41

Table 3

| Configuration<br>Value | Register | Recomm.<br>Default | Hardware<br>Default | Description                                                                                                                                      |

|------------------------|----------|--------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| abgl_hr[3:0]           | 1        | 5                  | 5                   | High resolution trim                                                                                                                             |

| auto10k                | 2        | 1                  | 1                   | Automatic calibration of the 10k oscillator every 0.6s by means of the 4 MHz quartz oscillator. May not be used in stretchedsingle mode          |

| avrate[9:0]            | 2        | 25                 | 1                   | Internal averaging rate                                                                                                                          |

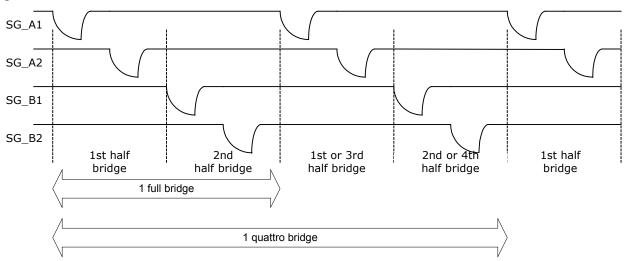

| bridge[1:0]            | 3        | 0                  | 0                   | O = not reasonable (one Halfbridge) 1 = 2 half bridges 2 = not supported 3 = 4 half bridges                                                      |

| calcor[7:0]            | 10       | 0                  | 0                   | Correction factor for TDC calibration value<br>cal := cal + calcor/8 = cal + [-127 to<br>+128]/8<br>= cal + [-15.875 to +16.000]                 |

| con_comp[1:0]          | 11       | 3                  | 3                   | Comparator switch-off mode  OO = off O1 = off between single measurements 10 = off during loading and between single measurements 11 = always on |

| cpu_speed[1:0]         | 0        | 3                  | 3                   | CPU ring oscillator speed  OO = fast  O1 = default  10 = slow  11 = very slow                                                                    |

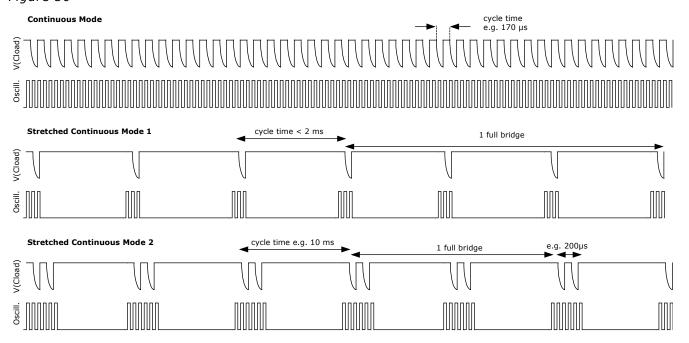

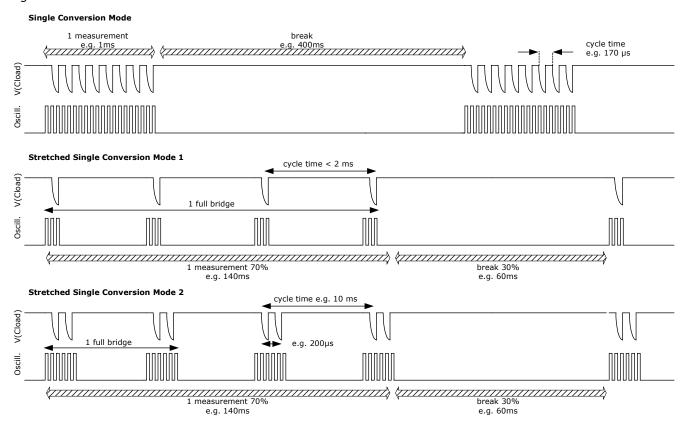

| cytime[7:0]            | 2        | 100                | 100                 | Cycle time in multiples 2 µs (8 * 4 MHz period, stretch = 0) or of 100 µs (10 kHz period, stretch = 1)                                           |

| Special interal Bits   | 0        | 0                  | 0                   | Use default                                                                                                                                      |

| dis_noise4             | 3        | 0                  | 0                   | Disable main noise unit                                                                                                                          |

| dis_osc_startup        | 0        | 1                  |                     | Reduce current when starting the oscillator                                                                                                      |

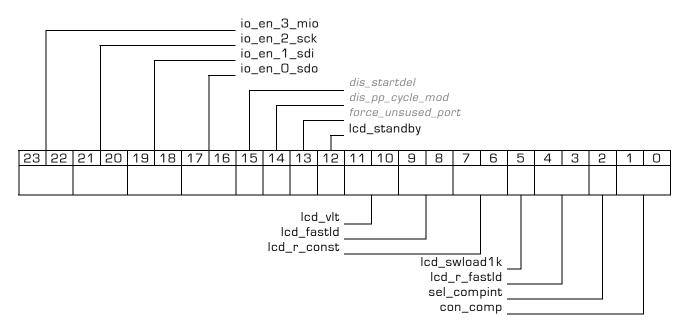

| dis_pp_cycle_mod       | 11       | 0                  | 0                   | Disable gain measurement with double cycle                                                                                                       |

| Configuration<br>Value | Register | Recomm.<br>Default | Hardware<br>Default | Description                                                                                                                                                                                                |

|------------------------|----------|--------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dis_startdel           | 11       | 1                  |                     | Disable start delay                                                                                                                                                                                        |

| en_avcal               | 1        | 0                  | 0                   | Enable TDC calibration value averaging by factor 16                                                                                                                                                        |

| en_wheatstone          | 3        | 0                  | 0                   | Enable Wheatstone mode                                                                                                                                                                                     |

| epr_pwr_cfg            | 1        | 0                  | 0                   | as frontend := 0<br>stand-alone := 1<br>Configuration in the EEprom is used after<br>a power-on reset                                                                                                      |

| epr_pwr_prg            | 1        | 0                  | 0                   | as frontend := 0<br>stand-alone := 1<br>Start user code at EEPROM address 48<br>after a power-on reset                                                                                                     |

| epr_usr_prg            | 1        | 0                  | 0                   | as frontend := 0<br>stand-alone := 1<br>Start user code at EEPROM address 48<br>after a measurement                                                                                                        |

| Special internal Bits  | 16       | 0                  | 0                   | Use default                                                                                                                                                                                                |

| force_unused_port      | 11       | 0                  | 0                   | force unused measurement ports to GND                                                                                                                                                                      |

| Special internal Bits  | 3        | 0                  | 0                   | Use default                                                                                                                                                                                                |

| io_a[3:0]              | 0        | 0                  | 0                   | I/O's<br>Output: output value, can be read back<br>Input: read input value                                                                                                                                 |

| io_en_O_sdo[1:0]       | 11       | 3                  | 2                   | Port definition  OO = output  O1 = input with pull-up  1O = input with pull-down  11 = input                                                                                                               |

| io_en_1_sdi[1:0]       | 11       | 3                  | 2                   | Port definition  OO = output  O1 = input with pull-up  1O = input with pull-down  11 = input                                                                                                               |

| io_en_2_sck[1:0]       | 11       | 3                  | 2                   | Port definition  OO = output  O1 = input with pull-up  1O = input with pull-down  11 = input                                                                                                               |

| io_en_3_mio[1:0]       | 11       | 3                  | 2                   | Port definition  OO = output  O1 = input with pull-up  1O = input with pull-down  11 = input                                                                                                               |

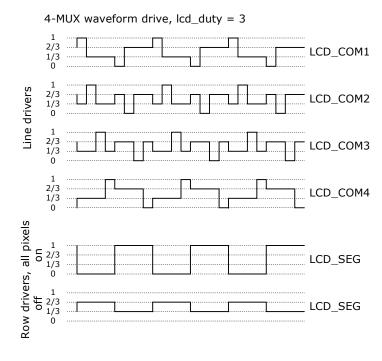

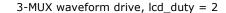

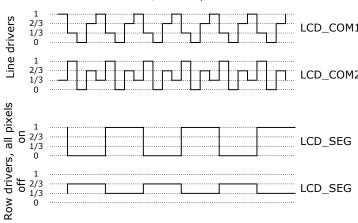

| lcd_duty[1:0]          | 1        | 0                  | 0                   | LCD duty cycle definition  O = off  1 = 1/2duty  2 = 1/3duty  3 = 1/4duty                                                                                                                                  |

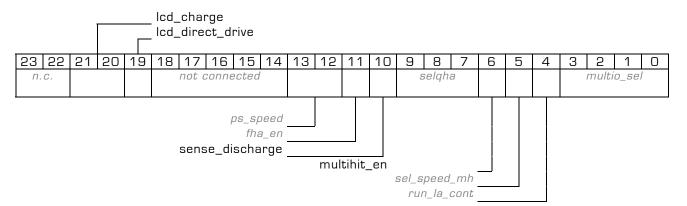

| Icd_charge[1:0]        | 16       | 0                  | 0                   | Selects number of LCD cycles before recharging  O = recharging each cycle  1 = recharging each 2 <sup>nd</sup> cycle  2 = recharging each 3 <sup>nd</sup> cycle  3 = recharging each 4 <sup>th</sup> cycle |

| Configuration<br>Value | Register | Recomm.<br>Default | Hardware<br>Default | Description                                                                          |

|------------------------|----------|--------------------|---------------------|--------------------------------------------------------------------------------------|

| lcd_directdrive        | 16       | 0                  |                     | Drive LCD directly from supply voltage                                               |

| lcd_fastId[1:0]        | 11       | 2                  | 2                   | Configures the number of fastload periods (10ms) with low-resistance voltage divider |

| lcd_freq[2:0]          | 1        | 4                  | 0                   | Select LCD frequency (switch-on time of pixels)                                      |

|                        |          |                    |                     | Pixel Time Multiplex mode                                                            |

|                        |          |                    |                     | 1/4 1/3 1/2 Hz                                                                       |

|                        |          |                    |                     | 0 8.0ms 15 20 31 Hz<br>1 4.8ms 26 34 52 Hz                                           |

|                        |          |                    |                     | 1 4.8ms 26 34 52 Hz<br>2 4.0ms 31 42 62 Hz                                           |

|                        |          |                    |                     | 3 3.2ms 30 52 78 Hz                                                                  |

|                        |          |                    |                     | 4 2.4ms 52 69 104 Hz                                                                 |

|                        |          |                    |                     | 5 2.0ms 62 83 125 Hz                                                                 |

|                        |          |                    |                     | 6 1.6ms 78 104 176 Hz                                                                |

|                        |          |                    |                     | 7 1.2ms 104 138 208 Hz                                                               |

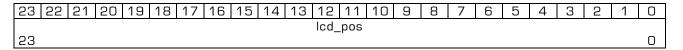

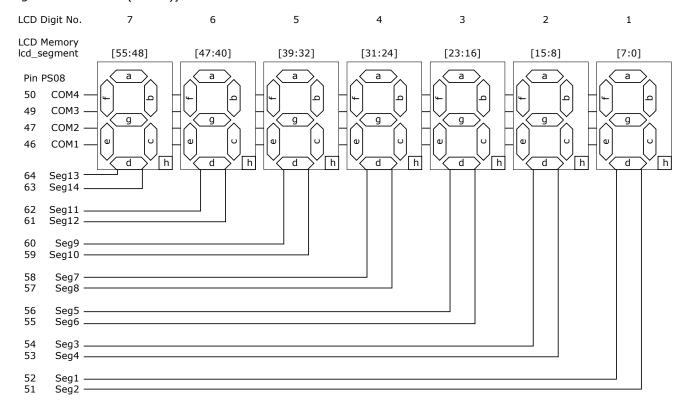

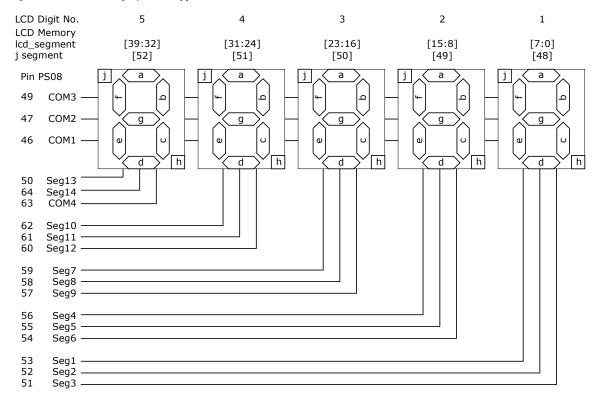

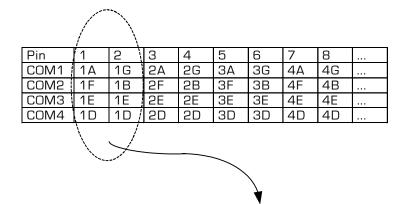

| lcd_pos[23:00]         | 12       | 076543210          | 076543210           | Position of LCD segments                                                             |

| lcd_r_const[1:0]       | 11       | 1                  | 0                   | Defines the cross resistance of the LCD voltage divider                              |

|                        |          |                    |                     | 0 = 15 k                                                                             |

|                        |          |                    |                     | 1 = 200 k                                                                            |

|                        |          |                    |                     | 2 = 800 k                                                                            |

|                        |          |                    |                     | 3 = 1600 k                                                                           |

| lcd_r_fastld[1:0]      | 11       | 0                  | 0                   | Selects the resistor for fast charging the                                           |

| '                      |          |                    |                     | LCD pixels                                                                           |

|                        |          |                    |                     | O = 15 k                                                                             |

|                        |          |                    |                     | 1 = 200 k                                                                            |

|                        |          |                    |                     | 2 = 800 k                                                                            |

|                        |          |                    |                     | 3 = 1600 k                                                                           |

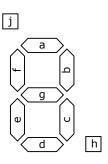

| lcd_segment[23:0]      | 13       | h000000            | h000000             | Display segments digits 2 to 0                                                       |

| lcd_segment[47:24]     | 14       | h000000            | h000000             | Display segments digits 5 to 3                                                       |

| lcd_segment[55:48]     | 15       | h000000            | h000000             | Display segments special characters (1/3                                             |

| lcd_standby            | 11       | 0                  | 0                   | and 1/4 duty)  O = LCD active                                                        |

| ·                      |          |                    |                     | 1 = LCD voltage supply in stand-by                                                   |

| lcd_swload1k           | 11       | 1                  | 1                   | LCD driver's voltage doubler uses 1 kOhm                                             |

|                        |          |                    |                     | instead of 200 Ohm to charge capacitor                                               |

| lcd_vlt[1:0]           | 11       | 1                  | 1                   | LCD voltage                                                                          |

|                        |          |                    |                     | 0 = 2 V                                                                              |

|                        |          |                    |                     | 1 = 2.5 V                                                                            |

|                        |          |                    |                     | 2 = 3 V                                                                              |

|                        | 4        | 0                  |                     | 3 = 2 V without pump                                                                 |

| low_batt[2:0]          | 1        | 0                  | U                   | Sets the voltage level for low battery                                               |

|                        |          |                    |                     | detection and EEpromwrite                                                            |

|                        |          |                    |                     | 2.2 V, 2.3 V, 2.4 V to 2.9 V                                                         |

| messb2                 | 1        | 0                  | П                   | [2.2 V + 0.1 V * low_batt] 1 = Set TDC Measurement range 2                           |

|                        |          |                    |                     | Sets the number of fake measurements                                                 |

| mfake[1:0]             | 3        | 0                  |                     | Sets the number of take measurements                                                 |

| Special internal bits  | 3        | 0                  | 1                   | Use recommended value                                                                |

|                        |          |                    |                     | Coo i coommondod valdo                                                               |

| mod_rspan              | 1        | 0                  | 0                   | 1 = Enable internal multiplication of gain                                           |

| _ ' ' ''               | ·        | ٦                  | _                   | compensation resistor Rspan                                                          |

| '                      | I        | I                  |                     | ,                                                                                    |

| Configuration        | Register | Recomm.  | Handwana | Description                                                               |

|----------------------|----------|----------|----------|---------------------------------------------------------------------------|

| Value                | Register | Default  | Default  | -                                                                         |

| mult_en_pp           | 1        | Delauit  |          | 1 = Enable multiplications in gain                                        |

| типо_от_рр           | 1 '1     |          |          | correction                                                                |

| mult_en_ub           | 1        | 0        | 0        | 1 = Enable multiplications for supply                                     |

|                      |          |          |          | voltage correction                                                        |

| Mult_Hb1[23:0]       | 4        | h100000  | h100000  | Multiplication factor for HB1 result                                      |

| Mult_Hb2[23:0]       | 5        | h100000  | հ100000  | h1 := h1 * [-2^23 to 2^23-1]/ 2^20  Multiplication factor for HB2 result  |

| ויומונ_ו וטבנבט.טן   |          | 11100000 | 11100000 | h1 := h1 * [-2^23 to 2^23-1]/ 2^20                                        |

| Mult_Hb3[23:0]       | 6        | h100000  | h100000  | Multiplication factor for HB3 result                                      |

| -                    |          |          |          | h1 := h1 * [-2^23 to 2^23-1]/ 2^20                                        |

| Mult_Hb4[23:0]       | 7        | h100000  | h100000  | Multiplication factor for HB4 result                                      |

| multio_sel[3:0]      | 16       | 12       |          | h1 := h1 * [-2^23 to 2^23-1]/ 2^20 Use multioO3 pin for diagnoses         |

| TTIGITIO_361[0.0]    | 10       | 1 =      | U        | O = multio                                                                |

|                      |          |          |          | 1 = clk1Okhz                                                              |

|                      |          |          |          | 2 = clkalu                                                                |

|                      |          |          |          | 3 = load                                                                  |

|                      |          |          |          | 4 = epr_acc<br>5 = portin_or                                              |

|                      |          |          |          | 6 = eprom read access                                                     |

|                      |          |          |          | 7 = testo_tdc                                                             |

|                      |          |          |          | 8 = phaseschifter out                                                     |

|                      |          |          |          | 9 = start_stop                                                            |

|                      |          |          |          | 10 = sense_ac1_comp2                                                      |

|                      |          |          |          | 11 = sense_schmitt_trigger                                                |

|                      |          |          |          | 12 = interrupt                                                            |

| High Resolution      | 16       | 1        | 1        | Switch high resolution, cannot be used with                               |

| Mult_PP[7:0]         | 10       | h80      | kon      | 1.5V Power Supply  Multiplication factor for gain correction              |

| Mult_PP[7.0]         | 10       | 1100     | 1100     | g := g * [0 to 255]/2^7                                                   |

| Mult_TkG[23:0]       | 8        | h100000  | h100000  | Amplification for Rspan correction                                        |

| Widio_TRO[E0.0]      |          | 1110000  | 1110000  | Rs := Rs * [-2^23 to 2^23-1]/ 2^20                                        |

| Mult_Tk0[23:0]       | 9        | h000000  | h000000  | Offset value for Rspan, directly                                          |

| NA 1: 111 17 01      | 1.0      | 1.00     |          | substracted                                                               |

| Mult_Ub[7:0]         | 10       | h00      | h80      | Multiplication factor for gain                                            |

|                      |          |          |          | compensation by means of voltage                                          |

|                      |          |          |          | measurement                                                               |

| Consist internal bit | 0        | 0        |          | $hb = hb/(1 + ub*[-128 to 127]/2^21)$                                     |

| Special internal bit | 3        | 0        | U        | Use default                                                               |

| osz10khz_fsos[5:0]   | 0        | h20      | h20      | Frequency trim of 10 kHz oscillator                                       |

| portpat              | 2        | 1        | 0        | Switch port patterns. 'On' stronly recommended                            |

| pptemp               | 2        | 0        | 0        | Enable gain error and temperature                                         |

|                      |          |          |          | measurement                                                               |

| Special internal bit | 3        | 0        |          | Use default                                                               |

| ps_qziel[5:0]        | 3        | 33       | 17       | Use recommended value                                                     |

| Special internal bit | 3        | 0        | 0        | Use default                                                               |

|                      |          |          |          |                                                                           |

| Special internal bit | 16       | 0        | 0        | Use default                                                               |

|                      |          | _        |          |                                                                           |

| rspan_by_temp        | 1        | 0        | 0        | Use temperature measurement instead of Rspan for temperature compensation |

| Special internal bit | 16       | 0        |          | Use default                                                               |

|                      |          |          |          |                                                                           |

| sel_compint          | 11       | 0        | 0        | 1 = Select internal comparator                                            |

**PICO**STRAIN

Single-chip Solution for Weight Scales

| Configuration<br>Value | Register | Recomm.<br>Default |    | Description                                                                                                                                                        |

|------------------------|----------|--------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sel_compr              | 0        | 0                  | 0  | Selects comparator working resistor $00 = 10k$ $01 = 10k$ $10 = 7k$ $11 = 4.1k$                                                                                    |

| Special internal bit   | 16       | 2                  | 2  | Use default                                                                                                                                                        |

| Special internal bit   | 16       | 0                  | 0  | Use default                                                                                                                                                        |

| sel_start_osz[2:0]     | 3        | 0                  | 0  | Sets delay from start of 4 MHz oscillator to start of measurement  0 = off 1 = continuously on 2 = 100 µs 3 = 200 µs 4 = 300 µs 5 = 400 µs 6 & 7 are not connected |

| sense_discharge        | 16       | 1                  | 0  | Set fast discharge of comparator's low-<br>pass capacitor                                                                                                          |

| single_conversion      | 2        | 0                  | 0  | O = Continuous mode 1 = Single conversion mode                                                                                                                     |

| speed_talu             | 1        | 0                  | 0  |                                                                                                                                                                    |

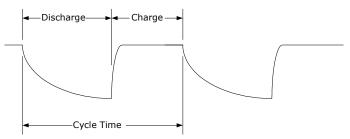

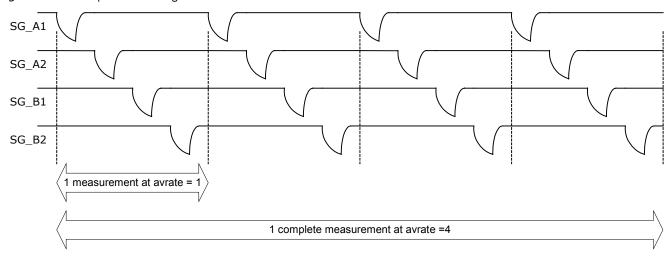

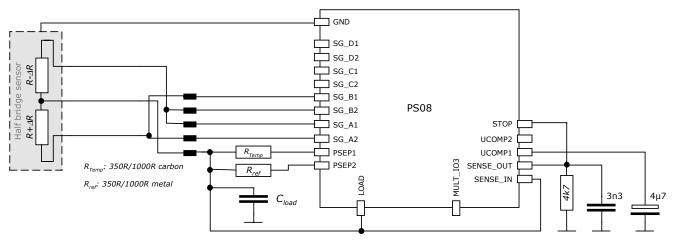

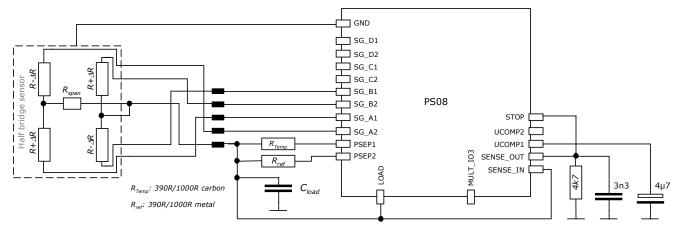

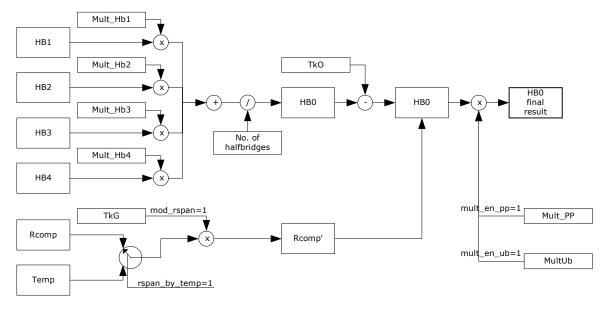

| stop_osz               | 3        | 0                  |    | Stop the oszillator by command (e.g. if there is no interrupt after AutoOn)                                                                                        |